【導(dǎo)讀】SoC性能指標(biāo)正在發(fā)生變化,從純性能指標(biāo)(GHz或MIPS)轉(zhuǎn)變?yōu)樾阅苄屎妥畹凸?。這一對于物聯(lián)網(wǎng)或移動設(shè)備至關(guān)重要的新指標(biāo)正成為汽車,嵌入式系統(tǒng)等各種應(yīng)用的關(guān)鍵。SoC設(shè)計團(tuán)隊(duì)可以利用硅IP實(shí)現(xiàn)復(fù)雜的電源管理,并且可以從經(jīng)驗(yàn)豐富的工程師提供的技術(shù)支持中獲益,從而縮短產(chǎn)品上市時間(TTM)和項(xiàng)目開發(fā)成本。

能效在半導(dǎo)體行業(yè)中成為關(guān)鍵

當(dāng)系統(tǒng)可以簡單地插入墻壁以接收電力時,復(fù)雜芯片產(chǎn)生的功耗不是真正的問題。最重要的功能是原始性能,以GHz或MIPS表示。然而,隨著2000年及以后無線移動設(shè)備的大量采用,該指標(biāo)趨于發(fā)生變化。對于電池供電的設(shè)備,兩次電池充電之間的時間幾乎與智能手機(jī)的MIPS電量一樣重要。

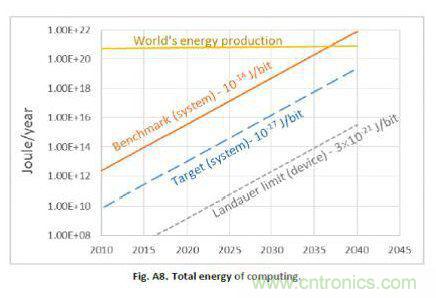

現(xiàn)在,讓我們退后一步,將半導(dǎo)體(和電子)行業(yè)視為功耗的來源,包括服務(wù)器,存儲,高功率計算(HPC),有線網(wǎng)絡(luò),4G和5G基站,這些應(yīng)用都需要高性能。半導(dǎo)體行業(yè)協(xié)會(SIA)和半導(dǎo)體研究公司(SRC)在2015年發(fā)布了“重啟IT革命:行動起來”報告,其中包括下圖:

圖1:計算的總能耗(來源:SIA)

顯然,數(shù)據(jù)中心是能耗大戶,其他應(yīng)用能耗(如汽車和物聯(lián)網(wǎng))也在提升,大多數(shù)物聯(lián)網(wǎng)IC都是在邊緣系統(tǒng)中。事實(shí)上,現(xiàn)在業(yè)界已經(jīng)接受將計算能力(CPU或DSP)納入邊緣系統(tǒng)的需求,因?yàn)橄蛏贤扑蛿?shù)據(jù)(到物聯(lián)網(wǎng)主站)和向下傳輸數(shù)據(jù)(一旦處理完數(shù)據(jù))顯然不是正確的選擇。而對于自動駕駛汽車等系統(tǒng),會出現(xiàn)不可接受的延遲:

本文中,我們將討論在成熟技術(shù)節(jié)點(diǎn)上開發(fā)的IC的多種應(yīng)用(與最先進(jìn)的節(jié)點(diǎn),如14/16 nm,10 nm或7 nm相對應(yīng)),在物聯(lián)網(wǎng),汽車,消費(fèi)電子等可能是也可能不是電池供電的。我們設(shè)定的目標(biāo)是:降低IC功耗,同時保持性能,縮減開發(fā)時間和成本,使用相同的IC,無需電源管理工作,識別潛在問題(噪聲容限,串?dāng)_等)。本文提出的解決方案可以實(shí)現(xiàn)這一目標(biāo),對TTM,成本和正確的功能沒有任何影響。

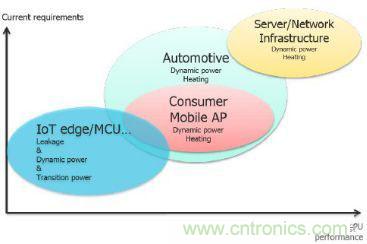

圖2:應(yīng)用中的電源問題

降低SoC功耗的各種解決方案

如上所述,自2000年以來,無線移動行業(yè)一直是電源管理技術(shù)的先驅(qū)。負(fù)責(zé)應(yīng)用處理器SoC的設(shè)計團(tuán)隊(duì)(如TI的OMAP,其次是高通,三星,蘋果等)已經(jīng)在系統(tǒng)級手機(jī)上實(shí)施了電源管理策略。電源管理技術(shù)非常復(fù)雜,以至于他們很快意識到在內(nèi)部電源管理功能(電源管理IC或PMIC)之上需要外部器件。這里的各種解決方案將在SoC內(nèi)部實(shí)施,不需要PMIC,因?yàn)槟繕?biāo)是保持成本與使用PMIC之前相同或更低的水平。

這里回顧一下可以降低SoC功耗的各種技術(shù)。

電源域管理

在實(shí)施任何特定的電力網(wǎng)絡(luò)IP或配電策略之前,首先要考慮定義電源域。請記住,電源域?qū)⒏鶕?jù)SoC中的功能塊進(jìn)行定義。一個功能塊可以涉及不同類型的單元,例如CPU和數(shù)字標(biāo)準(zhǔn)單元塊,它們一起與SRAM存儲器鏈接。這些模塊可以在不同的電壓下從不同的電源獲得電能。

定義了各種域,目標(biāo)是實(shí)現(xiàn)特定功率域的特定功率分配,并創(chuàng)建功率島。每個域可以與SoC的其余部分隔離并斷電(或上電),而不會影響其他電源域。我們將在本文后面看到如何部署此電源管理策略。

動態(tài)電壓頻率調(diào)節(jié)(DVFS)

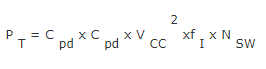

動態(tài)功耗由以下公式表示:

這里:

電源電壓和頻率的組合對總功耗具有立體影響,因?yàn)閯討B(tài)功耗具有對電壓的二次依賴性和對頻率的線性依賴性。智能節(jié)電解決方案可降低工作頻率,同時降低電源電壓。

主要思想是在給定頻率下盡可能降低電源電壓,同時仍保持某些功能的正確操作。電壓只能下降到某個臨界水平,超過此水平就會出現(xiàn)定時故障。

在應(yīng)用每功能DVFS方法時,假設(shè)已定義了每功能電源/時鐘域并實(shí)施了附加電路,SoC全局功耗可以明顯降低,同時保持性能相同或更好,以便當(dāng)其它功能保持靜默時需要用的功能可以正常運(yùn)行(即:降低電壓)。

筆記本電腦,服務(wù)器和移動設(shè)備廣泛采用動態(tài)電壓和頻率調(diào)節(jié)(DVFS)來節(jié)約能源,而DVFS在其他應(yīng)用(汽車,消費(fèi)電子......)的早期階段仍處于起步階段。根據(jù)實(shí)驗(yàn)結(jié)果,DVFS具有顯著的節(jié)能潛力。DVFS只是控制CMOS電路動態(tài)功耗的幾種方法之一。我們必須記住,它的使用會帶來一系列驗(yàn)證和實(shí)現(xiàn)挑戰(zhàn),但DVFS在降低動態(tài)模式下的SoC功耗方面非常有效。

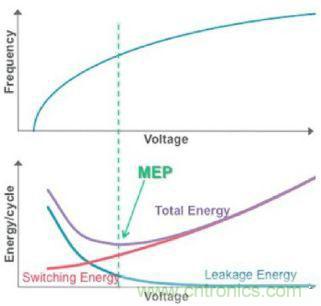

圖3:能耗(動態(tài)和漏電)與電壓的關(guān)系

接近閾值電壓

總功率是靜態(tài)或泄漏功率和動態(tài)功率的總合。隨著電壓朝向晶體管閾值電壓(Vt)下降,開關(guān)功率降低但同時漏電流增加。這意味著必須找到泄漏和開關(guān)電源之間的最佳組合,如圖3所示。

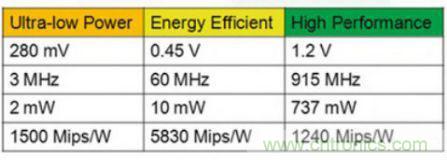

接近閾值電壓(NTV)將在提供最小能量的電壓范圍內(nèi)選擇(參見圖3),同時保持功能域工作。NTV是一種出色的電源管理技術(shù),在能效(EE)方面給出了非常好的結(jié)果,如圖4所示。這些結(jié)果來自對Intel Pentium的測量,我們可以注意到,0.45 V(接近閾值) ),EE達(dá)到每瓦5830 Mips,與額定電壓(1.2 V)為1240 Mips / Watt的EE進(jìn)行比較。第一個缺點(diǎn)可以在同一圖中看到:在標(biāo)稱電壓(1.2 V)下,芯片頻率達(dá)到915 MHz,而在NTV(0.45 V)時,它只有60 MHz。

NTV可提供出色的結(jié)果(功耗和能效),特別是在睡眠或觸發(fā)模式下,因?yàn)镾oC無需在此類模式下運(yùn)行完整性能,例如物聯(lián)網(wǎng)邊緣計算或永遠(yuǎn)在線傳感器。

圖4:能效與功能電壓

其他技術(shù):體偏置,GALS,......

GALS技術(shù)用于最大時鐘域管理效率。應(yīng)使用單向雙同步設(shè)備(如FIFO)實(shí)例化跨時鐘邊界,從而在不需要握手的情況下實(shí)現(xiàn)最佳延遲。可以沿著互連內(nèi)的任何鏈路劃分時鐘邊界,并且可以繞過GALS元件進(jìn)行同步操作。

電源和電壓域由電隔離層隔開,并且應(yīng)使用斷開技術(shù)關(guān)閉各個功能塊。當(dāng)電源域關(guān)閉時,特定功能塊必須保持狀態(tài)時,應(yīng)插入保留寄存器。

總之,GALS是一種高效但非??量蹋ㄔ诠こ碳墑e)的電源管理方法,它涉及特定的設(shè)計知識和應(yīng)用現(xiàn)有EDA工具的技巧。因此,在實(shí)施其他技術(shù)(如時鐘門控,電源域管理或DVFS)后,應(yīng)考慮GALS。

體偏置是一種芯片管理技術(shù),可以根據(jù)施加到芯片有源部分的電壓施加的襯底偏置電壓來降低功耗或提高性能。雖然理論上可以對任何襯底施加電壓,包括體積,但體偏置主要用于絕緣體上硅(SOI)晶圓。完全耗盡的SOI(FD-SOI)技術(shù)已經(jīng)引起了幾年的關(guān)注,幾家代工廠(三星,GlobalFoundries)和IDM(意法半導(dǎo)體)正在提供28 nm,22 nm和14 nm的ASIC功能。針對FDPower SOI技術(shù)的ASIC設(shè)計并不一定比散裝更復(fù)雜,但生態(tài)系統(tǒng)目前正致力于提供EDA工具和IP支持體偏置。

影響SoC完整性的各種電源問題

為了滿足激進(jìn)的功率預(yù)算目標(biāo),設(shè)計團(tuán)隊(duì)可能別無選擇,只能以極低的功率運(yùn)行,其直接影響是增加了關(guān)鍵信號對電磁(EM)串?dāng)_效應(yīng)的敏感性。

由于低功耗SoC具有小得多的噪聲容限,因此,開關(guān)活動可能導(dǎo)致電源傳輸網(wǎng)絡(luò)(PDN)振鈴并對芯片性能產(chǎn)生不利影響。

在今天的設(shè)計中,時鐘和配電網(wǎng)絡(luò)是集成電路故障的主要貢獻(xiàn)者,例如抖動,時鐘偏移,電遷移,耦合噪聲和功率分布下降。因此,性能和風(fēng)險規(guī)避都取決于時鐘和配電網(wǎng)絡(luò)設(shè)計的穩(wěn)健性,使得感應(yīng)和磁效應(yīng)的精確建模成為基本要求。

例如,一個給數(shù)字模塊供電的配電網(wǎng)絡(luò),該數(shù)字模塊具有高電流需求和非??斓拈_關(guān)活動(即,在非??斓乃矐B(tài)中吸收高電流峰值)。這樣的活動將導(dǎo)致配電網(wǎng)絡(luò)(PDN)上的振鈴,其與電感(L)和切換活動的速率(di / dt)成比例。隨著開關(guān)活動的增加,通過與PDN的耦合,振鈴的幅度將增加,以及關(guān)鍵或敏感的高頻或非常敏感的模擬信號上的噪聲水平。另一個挑戰(zhàn)是在模式轉(zhuǎn)換期間產(chǎn)生的低頻噪聲,這可能產(chǎn)生功能問題。

功率包括動態(tài)功率和漏電功率。動態(tài)功率取決于總負(fù)載電容,電源電壓和工作頻率。降低任何這些參數(shù)都會導(dǎo)致動態(tài)功耗降低。但PDN的一種常見設(shè)計方法是插入足夠的分頻來過濾網(wǎng)絡(luò)上的尖峰,因?yàn)殚_關(guān)噪聲會導(dǎo)致時鐘邊緣出現(xiàn)大電流尖峰。當(dāng)輸入信號的上升和下降時間期間CMOS柵極的NMOS和PMOS通道同時導(dǎo)通時,漏電功率是由電源和地之間的電流路徑引起的。

為了確保您的SoC設(shè)計不會受到電源或時鐘相關(guān)問題的影響,您必須從經(jīng)驗(yàn)豐富的工程師提供的技術(shù)支持中受益。與模擬設(shè)計一樣,沒有任何東西可以取代經(jīng)驗(yàn)。

在客戶的SoC中使用電源管理IP

實(shí)現(xiàn)電源域識別

我們首先需要定義SoC電源架構(gòu),因?yàn)檫@種架構(gòu)可以隨功能架構(gòu)變化。這將是設(shè)計人員識別屬于同一電源域的各種功能的首要任務(wù)。該功率域不是簡單地由電壓定義,而是與在給定功率模式下預(yù)期成為相同任務(wù)的一部分的各種塊的功能相關(guān)。

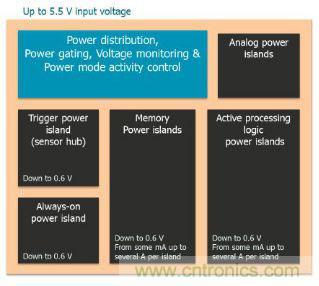

假設(shè)已經(jīng)定義了這種功率架構(gòu),SoC現(xiàn)在被劃分為N個域(N在5甚至更廣的范圍內(nèi))??梢葬槍﹄妷汗?yīng)(Vdd1至VddN)獨(dú)立地監(jiān)控這些域中的每一個,且設(shè)計者可以在SoC級實(shí)現(xiàn)功率分配和功率活動控制,在這種情況下,用于每個Vddn的獨(dú)立電網(wǎng)。在這個階段,Dolphin Integration可以提供由經(jīng)驗(yàn)豐富的SoC Architectural Experts(SAE)工程師提供的技術(shù)支持。這些工程師不是簡單的FAE,他們還在內(nèi)部管理電源管理實(shí)施,在內(nèi)部通過我們?yōu)榭蛻簦ㄔO(shè)計服務(wù))開發(fā)的SoC。其電源管理IP最多支持128個電源域。

圖5:SoC中的電源域

電源門控、控制和分配

在專家工程師的幫助下,設(shè)計團(tuán)隊(duì)已經(jīng)定義了各種電源域,現(xiàn)在是時候定義SoC電源架構(gòu),并在芯片中實(shí)現(xiàn)電源和時鐘分配。應(yīng)為每個電源域供電,插入電源門控以控制該域。通過開發(fā)的專利的電源島電源門控設(shè)備(名為CLICK),以及電壓域接口(VDIC),專家將幫助團(tuán)隊(duì)在各種電壓調(diào)節(jié)器(LDO和DC-DC)中選擇合適的方案,并將其組織為預(yù)先配置的硅IP庫。

我們還提出了一個支持高達(dá)5.5 V的過壓保護(hù)模塊。為了為該域提供時鐘,客戶將受益于超低功耗時鐘IP(名為Gamma)。使用正確的時鐘和配電設(shè)備至關(guān)重要,因?yàn)?ldquo;時鐘和配電網(wǎng)絡(luò)是集成電路故障機(jī)制的主要貢獻(xiàn)者,如抖動,時鐘偏移,電遷移,耦合噪聲和功率分布下降”,如上所述!

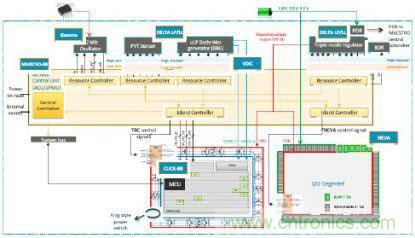

圖6:電源門控,控制和分配

芯片級SoC設(shè)計人員將選擇控制電源開關(guān),VREG或體偏置發(fā)生器和時鐘,電源網(wǎng)絡(luò)IP端口的所有部分,為SoC內(nèi)核供電。由于采用模塊化IP解決方案(名為MAESTRO),SoC電源模式控制的實(shí)現(xiàn)非常簡單。這些單元是精心設(shè)計的模塊,集成了內(nèi)置沖突管理功能,可防止SoC操作和轉(zhuǎn)換過程中出現(xiàn)故障。

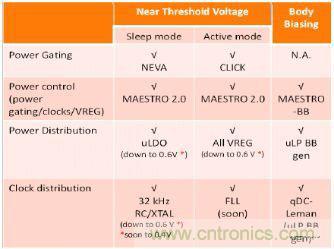

如果SoC設(shè)計用于本機(jī)閾值電壓(NTV)或DVFS操作,則集成IP產(chǎn)品組合在睡眠或工作模式下設(shè)計為具有本機(jī)NTV和DVFS支持,如圖6所示。

通過遵守結(jié)構(gòu)和裝配規(guī)則(命名為DELTA規(guī)則),確保了我們集成的完整電源管理IP產(chǎn)品的一致性。SoC設(shè)計人員可以通過采用類似的規(guī)則來利用他們自己的VREG的內(nèi)部開發(fā)來實(shí)現(xiàn)無縫的SoC集成。

集成電源管理IP允許提供on-SoC電源傳輸和電源模式控制,主要目標(biāo)是提供各種專家級的IP和技術(shù)支持,以實(shí)現(xiàn)節(jié)能(EE)SoC的最安全設(shè)計。由于我們工程師的這種專業(yè)知識,毫無疑問,與同一SoC的開發(fā)時間表相比,這種SoC設(shè)計將是最快的,因?yàn)殡娫垂芾硎怯稍O(shè)計團(tuán)隊(duì)首次集成而沒有任何支持。我們有信心保證這一最快的TTM能夠幫助客戶決定構(gòu)建節(jié)能SoC,以應(yīng)對像物聯(lián)網(wǎng)這樣的新興市場以及能源效率需求變得至關(guān)重要的成熟市場(汽車,消費(fèi)電子......)。

圖7:完整的電源管理IP集

時鐘分配

我們的時鐘IP允許實(shí)現(xiàn)始終在線的電源域,能夠在32 kHz接近閾值電壓下工作。根據(jù)目標(biāo)時鐘精度,時鐘源可以是基于晶體的或基于RC的。RC和XTAL振蕩器也可以組合在一起,以確保RC振蕩器的快速啟動,然后在運(yùn)行后切換到XTAL振蕩器。

由于RAM的電流保持與電壓成比例,因此將始終接通電源域的操作盡可能接近RAM(MDRV)的最小數(shù)據(jù)保持電壓,可確保SoC睡眠模式下的最低功耗。我們的穩(wěn)壓器庫包括一個超低靜態(tài)電壓調(diào)節(jié)器,其可編程輸出電壓低至0.6 V,其參考電壓不超過150 nA。

有效實(shí)現(xiàn)電源管理所需的專業(yè)知識

如前所述,重要的是重新評估這一點(diǎn),在處理電力(控制,門控或分配)時,專業(yè)知識是關(guān)鍵。那些參與SoC數(shù)字設(shè)計的人集成了一些模擬功能,他們知道在集成模擬時必須非常小心!我不僅討論模擬設(shè)計(這顯然是專家的任務(wù)),而且還涉及時鐘和功率分配,以及信號完整性保護(hù)。電源管理實(shí)施非常相似,只有專有技術(shù)和專業(yè)知識才能保證第一次正確的設(shè)計。

這就是為什么我們在PM專家提供的技術(shù)支持的基礎(chǔ)上,嘗試通過開發(fā)成熟的方法來進(jìn)一步幫助他們的客戶,這轉(zhuǎn)化為特定于電源管理的EDA工具的開發(fā),目標(biāo)是確定性地選擇正確的電源架構(gòu)和IP組件。這些是測試版,解決了所有電源管理實(shí)施步驟:

● PowerArchitect允許探索各種電源架構(gòu)并選擇最佳工作點(diǎn);

● PowerDesigner是一款自動化工具,用于生成頂級UPF,頂級RTL和ACU的RTL,采用頂級RTL的MAESTRO模塊UPF設(shè)計構(gòu)建;

● PowerVision是一種電源完整性驅(qū)動的SoC仿真工具。

處理電源管理和分配是一項(xiàng)非常艱巨的任務(wù),而且非常棘手!與數(shù)字設(shè)計不同,在開發(fā)完整的SoC(太大)時,不存在驗(yàn)證IP(VIP)和運(yùn)行模擬仿真(SPICE)。此外,我們可以要求數(shù)字設(shè)計師管理模擬仿真嗎?但是在選擇功率單元時做出稍微錯誤的決定可能會影響關(guān)鍵信號的完整性。在SoC中安全實(shí)施電源管理的最佳方法是詢問具有該領(lǐng)域?qū)I(yè)知識的工程師的專業(yè)知識,并將有助于創(chuàng)建最佳電源架構(gòu),并實(shí)施電源管理,從而使您的SoC變得高效節(jié)能。

結(jié)語

對于芯片制造商而言,高芯片功耗現(xiàn)在是電子行業(yè)任何領(lǐng)域的真正關(guān)注點(diǎn)。2000年前后,復(fù)雜的電源管理解決方案僅在的無線移動應(yīng)用中實(shí)施,當(dāng)下,為物聯(lián)網(wǎng),汽車或消費(fèi)類應(yīng)用實(shí)施這些解決方案變得非常必要。

但是,在SoC中實(shí)現(xiàn)高效的電源管理,對于首次使用SoC架構(gòu)的SoC架構(gòu)師來說可能會被認(rèn)為是復(fù)雜且有風(fēng)險的。很復(fù)雜,因?yàn)樗l(fā)現(xiàn)了各種功能,主要是模擬功能,而且他沒有接受過在SoC中選擇和實(shí)現(xiàn)它的培訓(xùn)。這就是為什么在做出錯誤選擇時影響設(shè)計進(jìn)度的風(fēng)險是真實(shí)的,導(dǎo)致錯過了這個快速發(fā)展的行業(yè)的主要風(fēng)險 - 上市時間(TTM)。

我們開發(fā)了一個完整的單元庫,用于在SoC中實(shí)現(xiàn)電源管理(電壓調(diào)節(jié)器,電源域接口調(diào)用,配電,時鐘分配等)。我們不僅僅是銷售這個庫,還會在項(xiàng)目開始時采取行動,通過提供經(jīng)驗(yàn)豐富的SoC架構(gòu)專家(SAE)的技術(shù)支持,幫助設(shè)計團(tuán)隊(duì)定義SoC電源架構(gòu)和實(shí)施策略。

本文轉(zhuǎn)載自半導(dǎo)體行業(yè)觀察。

推薦閱讀: