【導(dǎo)讀】 數(shù)據(jù)采樣過程通常是由時鐘信號的上升或者下降沿來觸發(fā)的。數(shù)據(jù)必須及時的到達(dá)接收端并且在接收器件開始鎖存之前穩(wěn)定為一個非模糊的邏輯狀態(tài)。任何數(shù)據(jù)的延遲或者波形的畸變將導(dǎo)致數(shù)據(jù)傳輸?shù)氖?。時序是高速系統(tǒng)的一切,信號時序取決于信號傳播的物理長度引起的延遲,同時取決于抵達(dá)閥值時波形的形狀。

本文主要介紹信號完整性是什么,信號完整性包括哪些內(nèi)容,什么時候需要注意信號完整性問題?

信號完整性是指高速產(chǎn)品設(shè)計(jì)中由互連線引起的所有問題。包括以下幾部分:

● 時序

● 噪聲

● 電磁干擾(EMI)

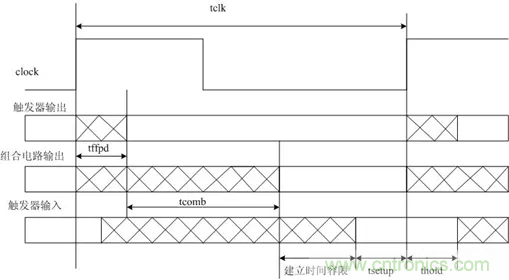

數(shù)據(jù)采樣過程通常是由時鐘信號的上升或者下降沿來觸發(fā)的。數(shù)據(jù)必須及時的到達(dá)接收端并且在接收器件開始鎖存之前穩(wěn)定為一個非模糊的邏輯狀態(tài)。任何數(shù)據(jù)的延遲或者波形的畸變將導(dǎo)致數(shù)據(jù)傳輸?shù)氖 r序是高速系統(tǒng)的一切,信號時序取決于信號傳播的物理長度引起的延遲,同時取決于抵達(dá)閥值時波形的形狀。信號波形畸變的原因可能有很多的原因。主要的包括建立時間Tsu、保持時間Th、輸出延時Tco、電路的線延遲Tdelay、時鐘延時Tpd等。

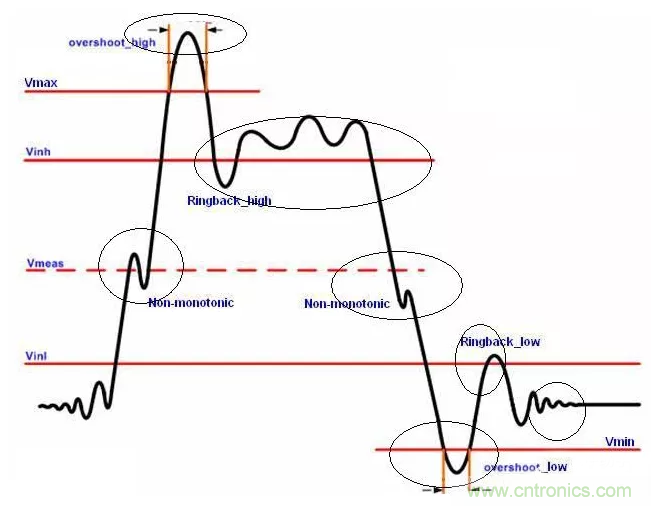

噪聲問題具體來說有很多種形式,例如:振鈴、反射、近端串?dāng)_、開關(guān)噪聲、非單調(diào)性、地彈,電源反彈、衰減、容性負(fù)載、靈敏度、有損線等等。

與噪聲有關(guān)的問題都可以從以下四個方面考慮:

● 單一網(wǎng)絡(luò)信號的完整性:在一個信號的信號路徑和返回路徑上由于阻抗突變引起的反射與失真。

● 兩個或多個網(wǎng)絡(luò)的串?dāng)_:多個信號通路之間耦合的互電容、互電感。

● 電源和地分配中的軌道塌陷:電源和地網(wǎng)絡(luò)中的阻抗壓降。

● 來自整個系統(tǒng)的電磁干擾輻射:來自元件、系統(tǒng)、外界的電磁干擾。

針對第一種情況,由于互聯(lián)線的阻抗發(fā)生變化,導(dǎo)致反射和失真(包括阻抗突變、反射、振鈴、ISI、時序等),解決的方法是:

● 使用均勻傳輸線;

● 進(jìn)行阻抗匹配。

針對第二種情況,由于兩個互連網(wǎng)絡(luò)之間的互容和互感引起容性耦合和感性耦合,而其中感性耦合占主導(dǎo)作用,對于感性耦合主導(dǎo)的噪聲,我們常常把這種串?dāng)_歸為開關(guān)噪聲、△I噪聲、dI-dt噪聲、地彈、同步開關(guān)噪聲(SSN)、同步開關(guān)輸出噪聲(SSO)。減小信號之間的串?dāng)_的方法如下:

● 采用介電質(zhì)常數(shù)比較小的材料;

● 減小互連線的長度,互連線越長,串?dāng)_越嚴(yán)重;

● 增加線之間的距離。

只要存在兩個電路,就會由于互容,一個電路的電壓產(chǎn)生電場,影響另一個電路;只要存在兩個電流回路,就會有互感,一個回路的電流產(chǎn)生磁場,影響另一個回路。

針對第三種情況,由于電壓越來越低,功耗越來越大,電源噪聲容限越來越小。因此在設(shè)計(jì)時要求電源阻抗低,地阻抗低,電源和地之間的阻抗低!所謂的低阻抗,在低頻時取決于電源線的電感,中頻時取決于板級的旁路電容,高頻時取決于片內(nèi)的分布電容陣列。具體的方法是:

● 相鄰電源和地分配層平面的的介質(zhì)應(yīng)該盡可能的薄,以使它們緊緊地靠近;

● 低電感的去耦電容;

● 封裝時安排多個很短的電源和地引腳;

● 片內(nèi)加去耦電容。

針對第四種情況,電磁干擾問題有三個方面:噪聲源、傳播路徑和天線。電磁干擾的強(qiáng)度和頻率正相關(guān),對于共模信號,電磁干擾強(qiáng)度和頻率成正比。對于差模信號,電磁干擾強(qiáng)度和頻率的平方成正比。

產(chǎn)生輻射的電壓源大多數(shù)來自電源分配網(wǎng)絡(luò)(由于PDN是電路板上最大的導(dǎo)體,因此也是最容易發(fā)射及接收噪聲),因此減少軌道塌陷也能降低輻射。解決的方法從如下三個方面入手:

● 首先從電路設(shè)計(jì)的角度解決;

● 其次從接口濾波的角度阻隔;

● 最后才從屏蔽的角度規(guī)避。

以上就是針對信號完整性的一個簡單的介紹,詳細(xì)的內(nèi)容以及分類方法各不相同,但具體問題的解決方法大都是相通的。

免責(zé)聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問題,請電話或者郵箱聯(lián)系小編進(jìn)行侵刪。