【導(dǎo)讀】功率氮化鎵 (GaN) 器件是電源設(shè)計人員工具箱內(nèi)令人激動的新成員�����。特別是對于想要深入研究GaN的較高開關(guān)頻率如何能夠?qū)е赂哳l率和更高功率密度的開發(fā)人員來說��。RF GaN是一項已大批量生產(chǎn)的經(jīng)驗證技術(shù)��,由于其相對于硅材料所具有的優(yōu)勢��,這項技術(shù)用于蜂窩基站和數(shù)款軍用/航空航天系統(tǒng)中的功率放大器��。本文將比較GaN FET與硅FET二者的退化機制�,并討論波形監(jiān)視的必要性。

使用壽命預(yù)測指標(biāo)

功率GaN落后于RF GaN的主要原因在于需要花時間執(zhí)行數(shù)個供貨商所使用的成本縮減策略�����。最知名的就是改用6英寸的硅基板�,以及更低成本的塑料封裝。對于電源設(shè)計人員來說��,理解GaN有可能帶來的性能提升��,以及某些會隨時間影響到最終產(chǎn)品性能的退化機制很重要�����。

聯(lián)合電子設(shè)備工程委員會 (JEDEC) 針對硅器件的認證標(biāo)準經(jīng)證明是產(chǎn)品使用壽命的很好預(yù)測指標(biāo)���,不過目前還沒有針對GaN的同等標(biāo)準���。要使用全新的技術(shù)來減輕風(fēng)險,比較謹慎的做法是看一看特定的用例����,以及新技術(shù)在應(yīng)用方面的環(huán)境限制,并且建立能夠針對環(huán)境變化進行應(yīng)力測試和監(jiān)視的原型機��。對于大量原型機的實時監(jiān)視會提出一些有意思的挑戰(zhàn),特別是在GaN器件電壓接近1000V��,并且dv/dts大于200V/ns時更是如此�����。

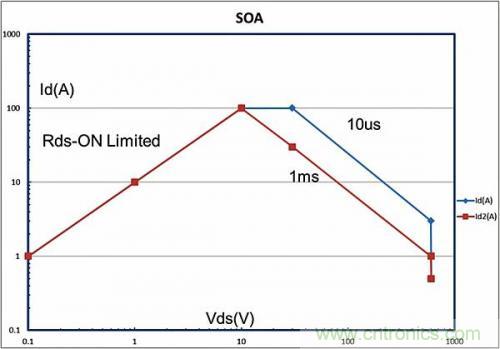

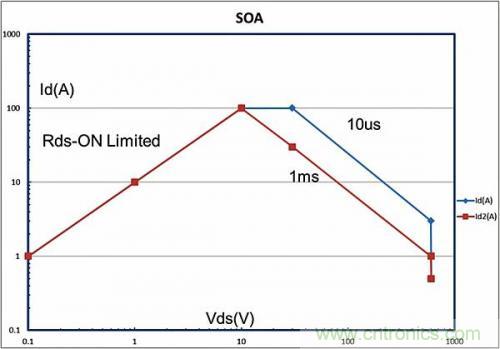

一個經(jīng)常用來確定功率FET是否能夠滿足目標(biāo)應(yīng)用要求的圖表是安全工作區(qū)域 (SOA) 曲線�。圖1中顯示了一個示例�。

圖1.GaN FET SOA曲線示例,此時Rds-On = 毫歐

硬開關(guān)設(shè)計

功率GaN FET被用在硬開關(guān)和數(shù)MHz的諧振設(shè)計中����。上面展示的零電壓 (ZVS) 或者零電流 (ZCS) 拓撲為數(shù)千瓦。SOA曲線的應(yīng)力最大的區(qū)域是右上角的電壓和電流最高的區(qū)域���。在這個硬開關(guān)區(qū)域內(nèi)運行一個功率GaN FET會導(dǎo)致由數(shù)個機制而造成的應(yīng)力增加�。最容易理解的就是熱應(yīng)力�����。例如��,在使用一個電感開關(guān)測試電路時��,有可能使器件從關(guān)閉時的電流幾乎為零、汲取電壓為幾百伏��,切換到接通時的電流幾乎瞬時達到10A�。

器件上的電壓乘以流經(jīng)的電流可以獲得瞬時功率耗散,對于這個示例來說����,在轉(zhuǎn)換中期可以達到500W以上。對于尺寸為5mm x 2mm的典型功率GaN器件����,這個值可以達到每mm2 50W。所以用戶也就無需對SOA曲線顯示的這個區(qū)域只支持短脈沖這一點而感到驚訝了����。由于器件的熱限值和封裝的原因,SOA曲線的右上部被看成是一個脈寬的函數(shù)�����。由于曲線中所見的熱時間常數(shù)����,更短的脈沖會導(dǎo)致更少的散熱。增強型封裝技術(shù)可被用來將結(jié)至環(huán)境的熱阻從大約15°C/W減小到1.2°C/W。由于減少了器件散熱�,這一方法可以擴大SOA。

SOA曲線

TI有一個系列的標(biāo)準占板面積的功率MOSFET���、DualCool™ 和NexFETs™�。這些MOSFET通過它們封裝頂部和底部散熱����,并且能夠提供比傳統(tǒng)占板面積封裝高50%的電流。這使得設(shè)計人員能夠靈活地使用更高電流��,而又無需增加終端設(shè)備尺寸�。與硅FET相比���,GaN FET的一個巨大優(yōu)勢就是可以實現(xiàn)的極短開關(guān)時間�。此外��,減少的電容值和可以忽略不計的Qrr使得開關(guān)損耗低很多�。在器件開關(guān)時,電壓乘以電流所得值的整數(shù)部分是器件必須消耗的功率�����。更低的損耗意味著更低的器件溫度和更大的SOA�。

SOA曲線所圈出的另外一個重要區(qū)域受到Rds-On的限制�����。在這個區(qū)域內(nèi)�����,器件上的電壓就是流經(jīng)器件的電流乘以導(dǎo)通電阻�����。在圖1所示的SOA曲線示例中��,Rds-On為100毫歐���。硅MOSFET的溫度取決于它們的Rds-On,這一點眾所周知����。在器件溫度從25ºC升高至大約100ºC時,它們的Rds-On幾乎會加倍��。

動態(tài)Rds-On

GaN FET具有一個復(fù)雜的Rds-On�,它是溫度,以及電壓和時間的函數(shù)。GaN FET的Rds-On對電壓和時間的函數(shù)依賴性被稱為動態(tài)Rds-On�����。為了預(yù)測一個GaN器件針對目標(biāo)使用的運行方式�,很有必要監(jiān)視這些動態(tài)Rds-On所帶來的影響。與SOA曲線的溫度引入應(yīng)力相類似����,電感硬開關(guān)應(yīng)力電路比較適合于監(jiān)視Rds-On。這是因為很多潛在的器件退化是與高頻開關(guān)和電場相關(guān)的�。

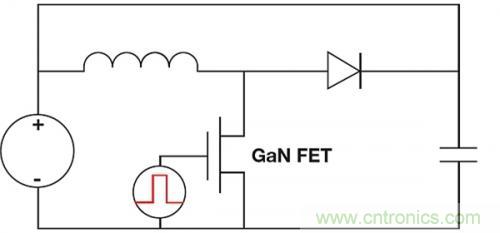

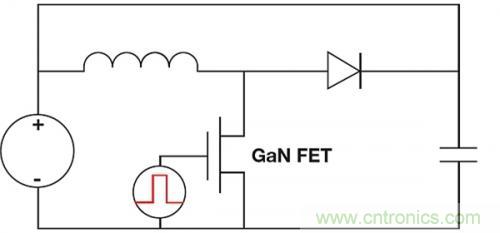

圖2是一個簡單開關(guān)電路,這個電路中給出了一種在SOA右上象限內(nèi)實現(xiàn)循環(huán)電流��,并對器件施加應(yīng)力的方法�����。

圖2.電感硬開關(guān)測試電路

寬帶隙

GaN是一種寬帶隙材料���,與硅材料的1.12eV的帶隙相比,它的帶隙達到3.4eV���。這個寬帶隙使得器件在被擊穿前�,能夠支持比同樣大小的硅器件高很多的電場。某些器件設(shè)計人員常用來幫助確定器件可靠性的測試有高溫反向偏置 (HTRB)�����、高溫柵極偏置 (HTGB) 和經(jīng)時電介質(zhì)擊穿 (TDDB)����。這些都是靜態(tài)測試,雖然在驗證器件設(shè)計有效性方面是好方法��,但是在高頻開關(guān)動態(tài)效應(yīng)占主導(dǎo)地位時,就不能代表典型使用情況�。高溫工作壽命 (HTOL) 是器件開關(guān)過程中的動態(tài)測試。特定的工作條件由制造商確定���,但是這些工作條件通常處于某些標(biāo)稱頻率、電壓和電流下����。

早期對于GaN針對RF放大器的使用研究發(fā)現(xiàn)了一個性能退化效應(yīng),此時器件能夠傳送的最大電流被減少為漏極電壓偏置的函數(shù)����。這個隨電壓變化的(捕獲引入)效應(yīng)被稱為“電流崩塌”。在緩沖器和頂層捕獲的負電荷導(dǎo)致電流崩塌或動態(tài)Rds-On增加�。在施加高壓時�����,電荷可被捕獲�,并且在器件接通時也許無法立即消散���。已經(jīng)采用了幾個器件設(shè)計技巧(電場板)來減少大多數(shù)靈敏GaN FET區(qū)域中的電場強度�。電場板已經(jīng)表現(xiàn)出能夠最大限度地減小RF GaN FET和開關(guān)功率GaN FET中的這種影響��。

GaN是一種壓電材料���。GaN器件設(shè)計人員通過添加一個晶格稍微不匹配的AIGaN緩沖層來利用這個壓電效應(yīng)��。這樣做增加了器件的應(yīng)力�,從而導(dǎo)致由自發(fā)和壓電效應(yīng)引起的極化場����。這個二維電子氣 (2DEG) 通道就是這個極化場的產(chǎn)物。具有2DEG通道的器件被稱為高電子遷移晶體管 (HEMT)�。不幸的是��,在器件運行時����,高外加電場也會導(dǎo)致有害的壓電應(yīng)力�,從而導(dǎo)致另外一種形式的可能的器件退化�����。對于諸如GaN的新技術(shù)來說��,擁有一個證明可靠性的綜合性方法很重要�����。如需了解與TI計劃相關(guān)的進一步細節(jié)�,請參考Sandeep Bahl的白皮書,一個限定GaN產(chǎn)品的綜合方法���。

為了降低成本��,功率GaN目前采用的是6英寸硅基板����。由于硅和GaN晶格不匹配�����,會出現(xiàn)線程脫位。這會導(dǎo)致晶格缺陷�����,并增加捕獲的可能性�����。這些捕獲的影響取決于它們的數(shù)量和在器件中的位置����。捕獲狀態(tài),占據(jù)或非占據(jù)�,也是施加的電場和時間的一個函數(shù)。捕獲充放電可能在最短100ns到最長數(shù)分鐘的時間范圍分布�。最接近柵極區(qū)域的捕獲充電和放電會調(diào)制器件的轉(zhuǎn)導(dǎo)。所有這些效應(yīng)是GaN FET的Rds-On的復(fù)雜電壓和時間相關(guān)性的基礎(chǔ)����。在限定期間,工程師通常在延長的期間內(nèi)對器件施加DC應(yīng)力�,并且定期移除這一應(yīng)力,以描述單個半導(dǎo)體測試的情況���。移除器件電壓偏置���,即使只有幾秒鐘的時間,也可以實現(xiàn)某些捕獲放電���,這樣的話����,就不會影響到與實際運行相關(guān)的動態(tài)Rds-On值了���。

總結(jié)

與硅FET相比��,功率GaN FET具有很多優(yōu)勢�����,比如說更低的開關(guān)損耗和更高的頻率切換能力�。更高的開關(guān)頻率可被用來增加系統(tǒng)的電源轉(zhuǎn)換密度���。要限定一個正在使用功率GaN FET的系統(tǒng)�,設(shè)計人員應(yīng)該了解可能的退化源����,并隨時監(jiān)視它們在溫度變化時的影響��。一個監(jiān)視動態(tài)Rds-ON增加的簡單方法就是測量時間和電壓變化過程中的轉(zhuǎn)換過程的效率�����。為了更好地了解損耗出現(xiàn)的位置����,系統(tǒng)被設(shè)計成能夠?qū)崟r監(jiān)視漏極����、柵極、源極和器件電流波形��。此系統(tǒng)能夠通過它們的SOA����,以1MHz以上的頻率,在電壓高達1000V和電流高達15A時��,硬開關(guān)FET���。

捕捉和分析實時波形可以幫助我們更好地理解高頻效應(yīng)��,比如說dv/dt��、柵極驅(qū)動器電感和電路板布局布線���,這些在基于GaN的設(shè)計中都很關(guān)鍵。監(jiān)視時間和溫度范圍內(nèi)趨勢變化的實時信息能夠為我們提供更好的GaN FET退化信息�����,并使我們對于更加智能器件和控制器產(chǎn)品的需求有深入的理解����。