【導(dǎo)讀】在本文上篇 文章中就使用電機(jī)驅(qū)動器 IC 設(shè)計PCB板提供了一些一般性建議,要求對 PCB 進(jìn)行精心的布局以實(shí)現(xiàn)適當(dāng)性能。在本文下篇中,將針對使用典型封裝的電機(jī)驅(qū)動器,提供一些具體的 PCB 布局建議。

引線封裝布局

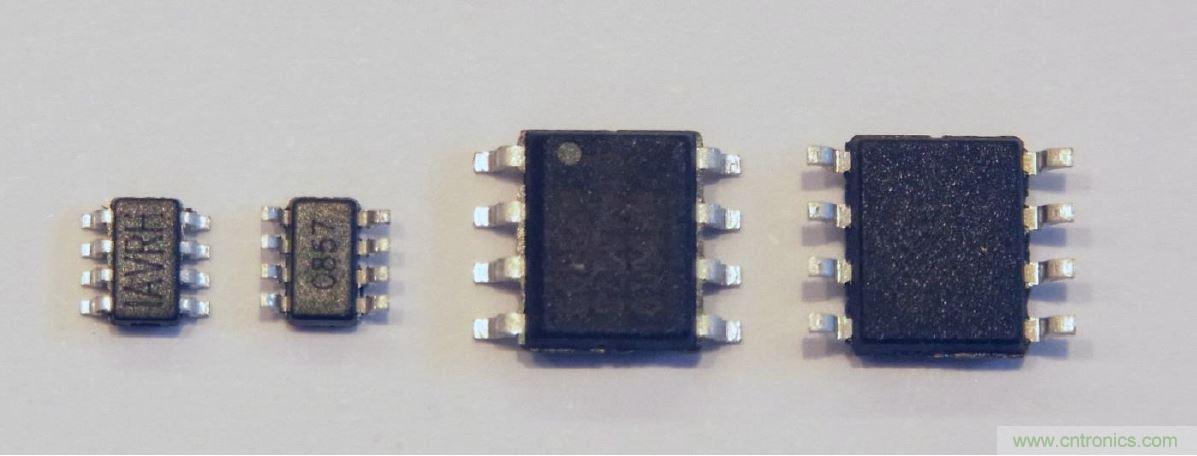

標(biāo)準(zhǔn)的引線封裝(如 SOIC 和 SOT-23 封裝)通常用于低功率電機(jī)驅(qū)動器中(圖 6)。

圖 6: SOT 23 和 SOIC 封裝

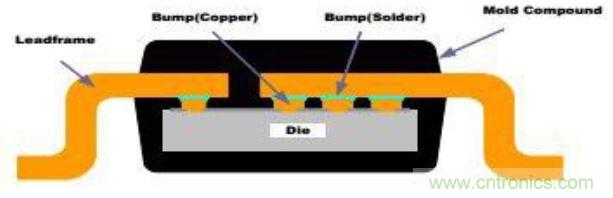

為了充分提高引線封裝的功耗能力,MPS公司采用 “倒裝芯片引線框架” 結(jié)構(gòu)(圖 7)。在不使用接合線的情況下,使用銅凸點(diǎn)和焊料將芯片粘接至金屬引線,從而可通過引線將熱量從芯片傳導(dǎo)至 PCB。

圖 7: 倒裝芯片引線框架

通過將較大的銅區(qū)域連接至承載較大電流的引線,可優(yōu)化熱性能。在電機(jī)驅(qū)動器 IC 上,通常電源、接地和輸出引腳均連接至銅區(qū)域。

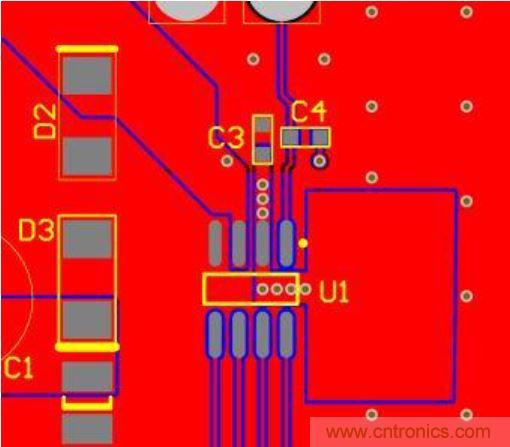

圖 8: 倒裝芯片 SOIC PCB 布局

圖 8 所示為“倒裝芯片引線框架”SOIC 封裝的典型 PCB 布局。引腳 2 為器件電源引腳。請注意,銅區(qū)域置于頂層器件的附近,同時幾個熱通孔將該區(qū)域連接至 PCB 背面的銅層。引腳 4 為接地引腳,并連接至表層的接地覆銅區(qū)。引腳 3(器件輸出)也被路由至較大的銅區(qū)域。

QFN 和 TSSOP 封裝

TSSOP 封裝為長方形,并使用兩排引腳。電機(jī)驅(qū)動器 IC 的 TSSOP 封裝通常在封裝底部帶有一個較大的外露板,用于排除器件中的熱量(圖9)。

圖 9: TSSOP 封裝

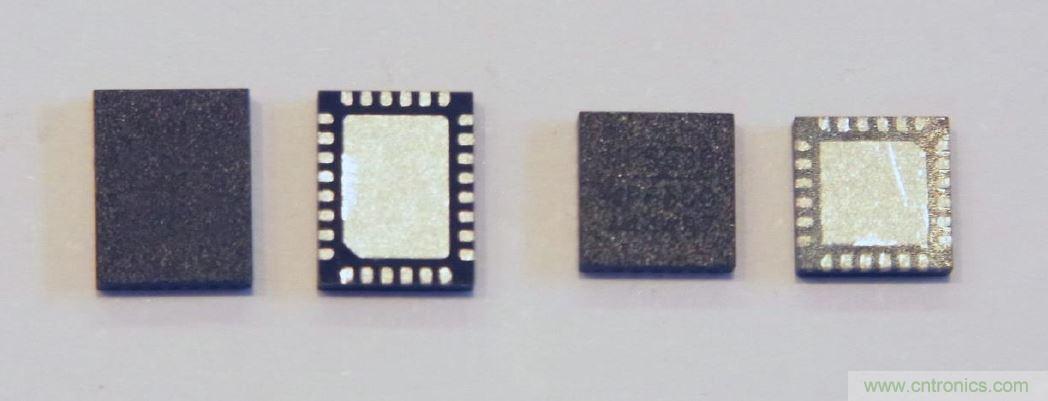

QFN 封裝為無引線封裝,在器件外緣周圍帶有板,器件底部中央還帶有一個更大的板(圖 10)。這個更大的板用于吸收芯片中的熱量。.

圖 10: QFN 封裝

為排除這些封裝中的熱量,外露板必須進(jìn)行良好的焊接。外露板通常為接地電位,因此可以接入 PCB 接地層。在圖 11 的 TSSOP 封裝的示例中,采用了一個 18 通孔陣列,鉆孔直徑為 0.38 mm。該通孔陣列的計算熱阻約為 7.7°C/W。

圖 11: TSSOP PCB 布局

通常,這些熱通孔使用 0.4 mm 及更小的鉆孔直徑,以防止出現(xiàn)滲錫。如果 SMT 工藝要求使用更小的孔徑,則應(yīng)增加孔數(shù),以盡可能保持較低的整體熱阻。

除了位于板區(qū)域的通孔,IC 主體外部區(qū)域也設(shè)有熱通孔。在 TSSOP 封裝中,銅區(qū)域可延伸至封裝末端之外,這為器件中的熱量穿過頂部的銅層提供了另一種途徑。

QFN 器件封裝邊緣四周的板避免在頂部使用銅層吸收熱量。必須使用熱通孔將熱量驅(qū)散至內(nèi)層或 PCB 的底層。

圖 12 中的 PCB 布局所示為一個小型的 QFN (4 × 4 mm) 器件。在外露板區(qū)域中,只容納了九個熱通孔。 (見圖 12) 因此,該 PCB 的熱性能不及圖 11 中所示的 TSSOP 封裝。

圖 12: QFN (4mmx4mm) 布局

倒裝芯片 QFN 封裝

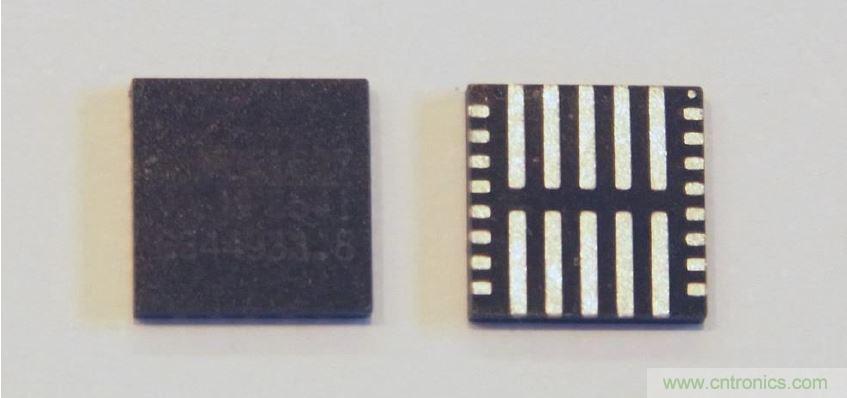

倒裝芯片 QFN (FCQFN) 封裝與常規(guī)的 QFN 封裝類似,但其芯片采取倒裝的方式直接連接至器件底部的板上,而不是使用接合線連接至封裝板上。這些板可以置于芯片上的發(fā)熱功率器件的反面,因此它們通常以長條狀而不是小板狀布置(見圖13)。

圖 13: FCQFN 封裝

這些封裝在芯片的表面采用了多排銅凸點(diǎn)粘接至引線框架(圖 14)。

圖 14: FCQFN 結(jié)構(gòu)

小通孔可置于板區(qū)域內(nèi),類似于常規(guī) QFN 封裝。在帶有電源和接地層的多層板上,通孔可直接將這些板連接至各層。在其他情況下,銅區(qū)域必須直接連接至板,以便將 IC 中的熱量吸入較大的銅區(qū)域中。

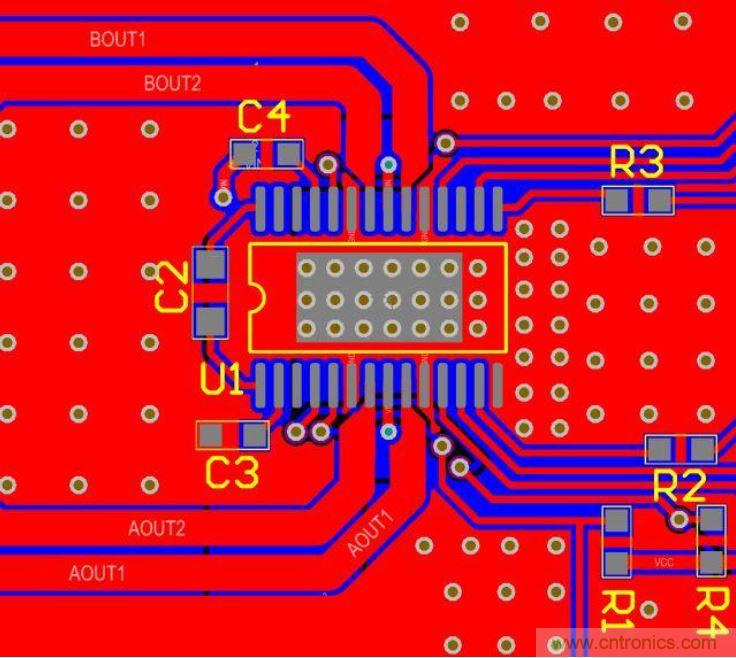

圖15: FCQFN PCB 布局

圖15 顯示了所示為 MPS 公司的功率級 IC MP6540 。該器件具有較長的電源和接地板,以及三個輸出口。請注意,該封裝只有 5mmx5mm。

器件左側(cè)的銅區(qū)域為功率輸入口。這個較大的銅區(qū)域直接連接至器件的兩個電源板。

三個輸出板連接至器件右側(cè)的銅區(qū)域。注意銅區(qū)域在退出板之后盡可能地擴(kuò)展。這樣可以充分將熱量從板傳遞到環(huán)境空氣中。

同時,注意器件右側(cè)兩個板中的數(shù)排小通孔。這些板均進(jìn)行了接地,且 PCB 背面放置了一個實(shí)心接地層。這些通孔的直徑為 0.46 mm,鉆孔直徑為 0.25 mm。通孔足夠小,適合置于板區(qū)域內(nèi)。

綜上所述,為了使用 電機(jī)驅(qū)動器 IC實(shí)施成功的 PCB 設(shè)計,必須對 PCB 進(jìn)行精心的布局。因此,本文提供了一些實(shí)用性的建議,以期望可以幫助 PCB 設(shè)計人員實(shí)現(xiàn)PCB板良好的電氣和熱性能。

推薦閱讀: