【導(dǎo)讀】逐次逼近型模數(shù)轉(zhuǎn)換器(因其逐次逼近型寄存器而稱為SAR ADC)廣泛運(yùn)用于要求最高18 位分辨率和最高5 MSPS 速率的應(yīng)用中。其優(yōu)勢包括尺寸小、功耗低、無流水線延遲和易用。主機(jī)處理器可以通過多種串行和并行接口(如SPI、I2C 和LVDS)訪問或控制ADC。本文將討論打造可靠、完整數(shù)字接口的設(shè)計技術(shù),包括數(shù)字電源電平和序列、啟動期間的I/O 狀態(tài)、接口時序、信號質(zhì)量以及數(shù)字活動導(dǎo)致的誤差。

數(shù)字I/O 電源電平和序列

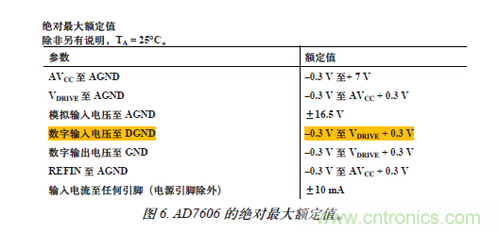

M多數(shù)SAR ADC 都提供獨(dú)立的數(shù)字I/O 電源輸入(VIO 或VDRIVE),后者決定接口的工作電壓和邏輯兼容性。此引腳應(yīng)與主機(jī)接口(MCU、DSP 或FPGA)電源具有相同的電壓。數(shù)字輸入一般應(yīng)在DGND − 0.3 V 與VIO + 0.3 V 之間,以避免違反絕對最大額定值。須在VIO 引腳與DGND 之間連接走線短的去耦電容。

采用多個電源的ADC 可能擁有明確的上電序列。應(yīng)用筆記 AN-932《電源時序控制》為這些ADC 電源的設(shè)計提供了良好的參考。為了避免正向偏置ESD 二極管,避免數(shù)字內(nèi)核加電時處于未知狀態(tài),要在接口電路前打開I/O 電源。模擬電源通常在I/O電源之前加電,但并非所有ADC 均是如此。請參閱并遵循數(shù)據(jù)手冊中的內(nèi)容,確保序列正確。

啟動期間的數(shù)字I/O 狀態(tài)

為了確保初始化正確無誤,有些SAR ADC 要求處于某些邏輯狀態(tài)或序列,以實現(xiàn)復(fù)位、待機(jī)或關(guān)斷等數(shù)字功能。在所有電源都穩(wěn)定之后,應(yīng)施加指定脈沖或組合,以確保ADC 啟動時的狀態(tài)符合預(yù)期。例如,一個高脈沖在RESET 上持續(xù)至少50 ns,這是配置 AD7606 以使其在上電后能正常運(yùn)行所必須具備的條件。

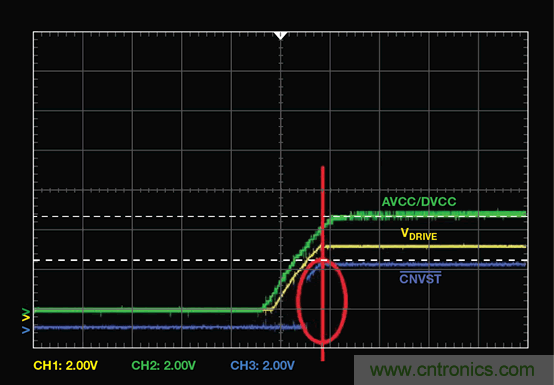

在所有電源均完全建立之前,不得切換數(shù)字引腳。對于SAR ADC,轉(zhuǎn)換開始引腳CNVST 可能對噪聲敏感。在圖1 所示示例中,當(dāng)AVCC、DVCC 和VDRIVE 仍在上升時,主機(jī)cPLD 拉高CNVST。這可能使 AD7367 進(jìn)入未知狀態(tài),因此,在電源完全建立之前,主機(jī)應(yīng)使 CNVST 保持低電平。

圖1. 在電源上升時拉高 CNVST 可能導(dǎo)致未知狀態(tài)。

數(shù)字接口時序

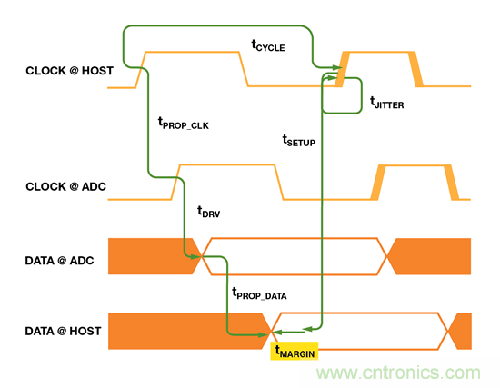

轉(zhuǎn)換完成之后,主機(jī)可以通過串行或并行接口讀取數(shù)據(jù)。為了正確讀取數(shù)據(jù),須遵循特定的時序策略,比如,SPI 總線需要采用哪種模式等。不得違反數(shù)字接口時序規(guī)范,尤其是ADC 和主機(jī)的建立和保持時間。最大比特率取決于整個循環(huán),而不僅僅是最小額定時鐘周期。圖2 和下列等式展示了如何計算建立和保持時間裕量。主機(jī)把時鐘發(fā)送至ADC 并讀取ADC 輸出的數(shù)據(jù)。

圖2. 建立和保持時序裕量

tCYCLE = tJITTER + tSETUP + tPROP_DATA + tPROP_CLK + tDRV + tMARGIN

tCYCLE : 時鐘周期 = 1/fCLOCK

tJITTER: 時鐘抖動

tSETUP: 主機(jī)建立時間

tHOLD: 主機(jī)保持時間

tPROP_DATA: 從ADC 到主機(jī)的傳輸線路的數(shù)據(jù)傳播延遲

tPROP_CLK: 從主機(jī)到ADC 的傳輸線路的數(shù)據(jù)傳播延遲

tDRV: 時鐘上升/下降沿后的數(shù)據(jù)輸出有效時間

tMARGIN: Margin time, ≥ 裕量時間大于等于0 表示達(dá)到建立時間或保持時間要 求,小于0 表示未達(dá)到建立時間或保持時間要求。

主機(jī)建立時間裕量

tMARGIN_SETUP = tCYCLE, min – tJITTER – tSETUP – tPROP_DATA – tPROP_CLK – tDRV, MAX

建立時間等式以最大系統(tǒng)延遲項定義最小時鐘周期時間或最大頻率。要達(dá)到時序規(guī)格,必須大于等于0。提高周期(降低時鐘頻率)以解決系統(tǒng)延遲過大問題。對于緩沖器、電平轉(zhuǎn)換器、隔離器或總線上的其他額外元件,把額外延遲加入tPROP_CLK 和tPROP_DATA。

tMARGIN_HOLD = tPROP_DATA + tPROP_CLK + tDRV – tJITTER – tHOLD

保持時間等式規(guī)定了最小系統(tǒng)延遲要求,以避免因違反保持時間要求而出現(xiàn)邏輯錯誤。要達(dá)到時序規(guī)格,必須大于等于0。

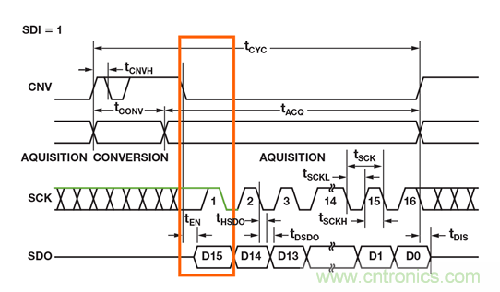

ADI 公司帶SPI 接口的許多SAR ADC 都是從 CS 或CNV 的下降沿為MSB 提供時鐘信號,剩余的數(shù)據(jù)位則跟隨SCLK 的下降沿,如圖3 所示。在讀取MSB 數(shù)據(jù)時,要使用等式中的tEN 而非tDRV。

圖3. AD7980 3 線 CS 模式下的SPI 時序。

因此,除了最大時鐘速率以外,數(shù)字接口的最大工作速率也取決于建立時間、保持時間、數(shù)據(jù)輸出有效時間、傳播延遲和時鐘抖動。

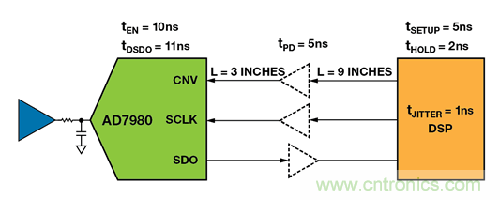

在圖4 中,DSP 主機(jī)訪問 AD7980 處于3 線 CS 模式下,其中,VIO = 3.3 V。DSP 鎖存SCLK 下降沿上的SDO 信號。DSP 的額定最小建立時間為5 ns,最小保持時間為2 ns。對于典型的FR-4PCB 板,傳播延遲約為180 ps/in。緩沖器的傳播延遲為5 ns。CNV、SCLK 和SDO 的總傳播延遲為

tprop = 180 ps/in × (9 in + 3 in) + 5 ns = 7 ns.

tJITTER = 1 ns. 主機(jī)SCLK 的工作頻率為30 MHz,因此, tCYCLE = 33 ns.

tSETUP_MARGIN = 33 ns − 1 ns – 5 ns – 7 ns – 11 ns – 7 ns = 2 ns

tHOLD_MARGIN =11 ns + 7 ns + 7 ns – 1 ns – 2 ns = 22 ns

建立時間和保持時間裕量均為正,因此,SPI SCLK 可以在30 MHz 下工作。

圖4. DSP 和AD7980 之間的數(shù)字接口

數(shù)字信號質(zhì)量

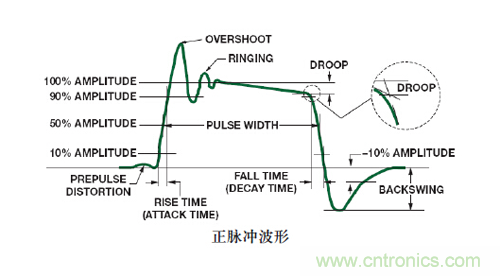

數(shù)字信號完整性(包括時序和信號質(zhì)量)確保:在額定電壓下接收信號;不相互干擾;不損壞其他器件;不污染電磁頻譜。信號質(zhì)量由多個項定義,如圖5 所示。本部分將介紹過沖、振鈴、反射和串?dāng)_。

圖5. 常用信號質(zhì)量規(guī)格

反射是阻抗不匹配導(dǎo)致的結(jié)果。當(dāng)信號沿著走線傳播時,每個接口處的瞬時阻抗都不相同。部分信號會反射回去,部分信號會繼續(xù)沿著線路傳播。反射可能在接收器端產(chǎn)生過沖、欠沖、振鈴和非單調(diào)性時鐘邊沿

過沖和欠沖可能損壞輸入保護(hù)電路,或者縮短IC 的使用壽命。圖6 所示為 AD7606 的絕對最大額定值。數(shù)字輸入電壓應(yīng)在–0.3 V 和VDRIVE + 0.3 V 之間。另外,如果振鈴高于最大VIL 或小于最小VIH 可能導(dǎo)致邏輯誤差。

圖6. AD7606 的絕對最大額定值

為了減少反射:

盡量縮短走線的長度

控制走線的特性阻抗

消除分支

使用適當(dāng)?shù)亩私臃桨?/div>

用環(huán)路面積小的固體金屬作為返回電流參考平面

使用較低的驅(qū)動電流和壓擺率

針對走線特性阻抗的計算,目前有許多軟件工具或網(wǎng)站,比如Polar Instruments Si9000 PCB 傳輸線路場求解器。借助這些工具,特性阻抗計算起來非常簡單,只需選擇傳輸線路型號并設(shè)置相應(yīng)的參數(shù)即可,比如電介質(zhì)類型和厚度以及走線寬度、厚度和隔 離。

作為一種新興標(biāo)準(zhǔn),IBIS 用于描述IC 數(shù)字I/O 的模擬行為。ADI提供針對SAR ADC 的IBIS 模型。預(yù)布局仿真可檢測時鐘分布、芯片封裝類型、電路板堆疊、網(wǎng)絡(luò)拓?fù)浣Y(jié)構(gòu)和端接策略。也可檢測串行接口時序限制以便為定位和布局提供指導(dǎo)。后仿真可驗證 設(shè)計是否符合所有指導(dǎo)方針和限制的要求,同時檢測是否存在反射、振鈴、串?dāng)_等違反要求的情況。

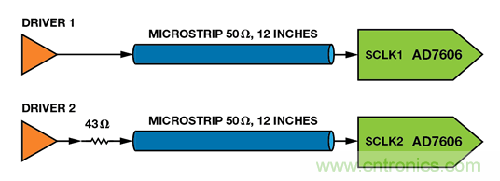

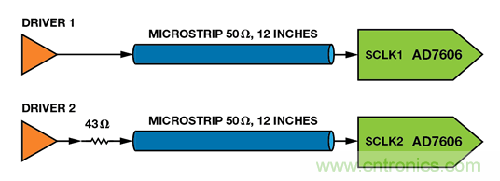

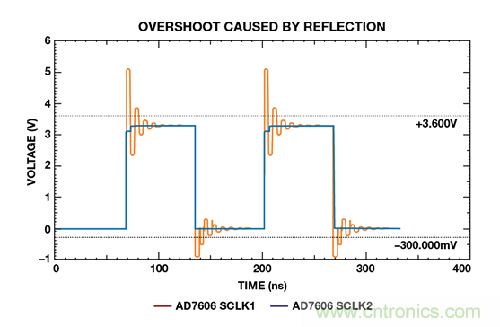

在圖7 中,一個驅(qū)動器通過一條12 英寸的微帶線路連接SCLK1,另一個驅(qū)動器通過一個與微帶串聯(lián)的43 Ω 電阻連接SCLK2。

圖7. 驅(qū)動AD7606 SCLK

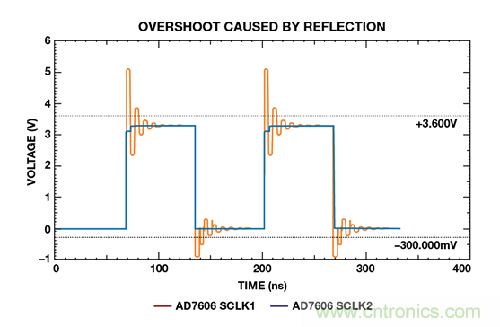

在圖8 中,SCLK1 上的大過沖違反了–0.3 V 至+3.6 V 的絕對最大額定值。串聯(lián)電阻可減小SCLK2 上的壓擺率,使信號處于額定值之內(nèi)。

圖8. AD7606 IBIS 過沖模型仿真

串?dāng)_是能量通過互電容(電場)或互感(磁場)在并行傳輸線路間耦合的情況。串?dāng)_量取決于信號的上升時間、并行線路的長度以及它們之間的間距。

控制串?dāng)_的一些常用方法為:

增加線路間距

減小并行布線

使走線靠近參考金屬平面

使用適當(dāng)?shù)亩私臃桨?/div>

減小信號壓擺率

數(shù)字活動導(dǎo)致的性能下降

數(shù)字活動可能導(dǎo)致SAR ADC 性能下降,使SNR 因數(shù)字地或電源噪聲、采樣時鐘抖動和數(shù)字信號干擾而減小。

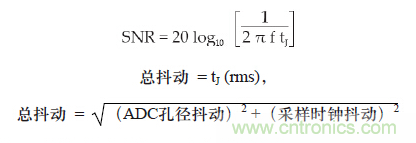

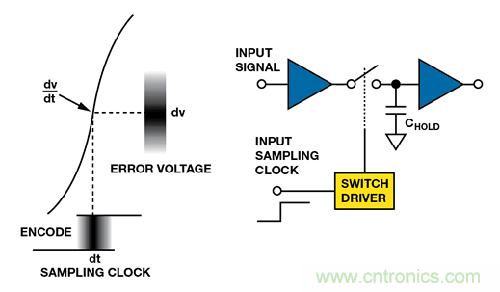

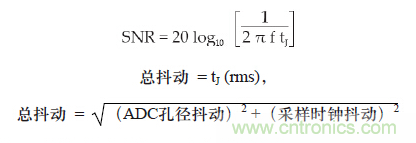

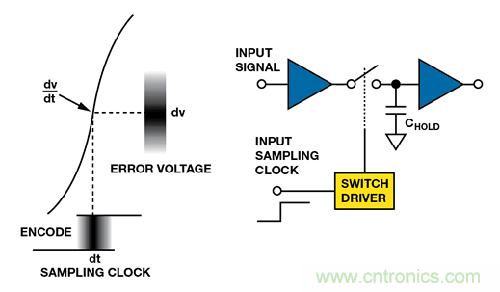

孔徑或采樣時鐘抖動設(shè)定SNR 限值,尤其是對高頻輸入信號。系統(tǒng)抖動有兩個來源:來自片內(nèi)采樣保持電路的孔徑抖動(內(nèi)部抖動),以及采樣時鐘上的抖動(外部抖動)。孔徑抖動為轉(zhuǎn)換間的 采樣時間變化,為ADC 的函數(shù)。采樣時鐘抖動通常為主要誤差源,但兩個源都會導(dǎo)致模擬輸入采樣時間變化,如圖9所示。它們的影響難以區(qū)分。

總抖動會產(chǎn)生誤差電壓,ADC 總SNR 的限制因素為

其中,f 為模擬輸入頻率,tJ 為總時鐘抖動。

例如,當(dāng)模擬輸入為10 kHz,總抖動為1 ns 時,SNR 限值為84 dB。

圖9. 采樣時鐘抖動導(dǎo)致的誤差電

數(shù)字輸出開關(guān)導(dǎo)致的電源噪聲應(yīng)與敏感的模擬電源相隔離。分別去耦模擬和數(shù)字電源,密切注意地回流路徑。

高精度SAR ADC 可能對數(shù)字接口上的活動很敏感,即使電源適當(dāng)去耦和隔離時。突發(fā)時鐘往往優(yōu)于連續(xù)時鐘。數(shù)據(jù)手冊通常會列出接口不應(yīng)活動的安靜時間。在較高吞吐速率條件下,可能難以減少這些時間內(nèi)的數(shù)字活動,通常為采樣時刻及出現(xiàn)關(guān)鍵位判斷點(diǎn)時。

結(jié)論

密切注意數(shù)字活動,確保SAR ADC 轉(zhuǎn)換有效。數(shù)字活動導(dǎo)致的誤差可能使SAR ADC 進(jìn)入未知狀態(tài),導(dǎo)致故障,或者降低性能。希望本文能幫助設(shè)計師排查根本原因,同時還能提供解決方案。

特別推薦

- 毫秒級響應(yīng):新一代數(shù)字音頻遠(yuǎn)距離實時傳輸方案解析

- RIGOL高速伺服激光加工系統(tǒng)MIPI D-PHY一致性測試

- 無感FOC算法驅(qū)動的BLDC電機(jī)的優(yōu)勢解析與實戰(zhàn)應(yīng)用方案

- 詳解超級電容器與電池在儲能解決方案的對比 (上)

- 從噪聲抑制到功耗優(yōu)化:CTSD如何重塑現(xiàn)代信號鏈架構(gòu)

- Wi-Fi 7頻率控制核心密碼:三大關(guān)鍵器件深度解析

- 用于電動汽車車載充電器的 CLLLC 與 DAB 比較

技術(shù)文章更多>>

- 從噪聲抑制到功耗優(yōu)化:CTSD如何重塑現(xiàn)代信號鏈架構(gòu)

- 詳解超級電容器與電池在儲能解決方案的對比 (上)

- 無感FOC算法驅(qū)動的BLDC電機(jī)的優(yōu)勢解析與實戰(zhàn)應(yīng)用方案

- RIGOL高速伺服激光加工系統(tǒng)MIPI D-PHY一致性測試

- 毫秒級響應(yīng):新一代數(shù)字音頻遠(yuǎn)距離實時傳輸方案解析

技術(shù)白皮書下載更多>>

- 車規(guī)與基于V2X的車輛協(xié)同主動避撞技術(shù)展望

- 數(shù)字隔離助力新能源汽車安全隔離的新挑戰(zhàn)

- 汽車模塊拋負(fù)載的解決方案

- 車用連接器的安全創(chuàng)新應(yīng)用

- Melexis Actuators Business Unit

- Position / Current Sensors - Triaxis Hall

熱門搜索

精密電阻

精密工具

景佑能源

聚合物電容

君耀電子

開發(fā)工具

開關(guān)

開關(guān)電源

開關(guān)電源電路

開關(guān)二極管

開關(guān)三極管

科通

可變電容

可調(diào)電感

可控硅

空心線圈

控制變壓器

控制模塊

藍(lán)牙

藍(lán)牙4.0

藍(lán)牙模塊

浪涌保護(hù)器

雷度電子

鋰電池

利爾達(dá)

連接器

流量單位

漏電保護(hù)器

濾波電感

濾波器