【導(dǎo)讀】本設(shè)計實現(xiàn)了一種基于片上系統(tǒng)現(xiàn)場可編程門陣列(SoC FPGA) 的心電信號(ECG)檢測系統(tǒng)。系統(tǒng)通過具有高輸入阻抗、高共模抑制比和低噪聲的前置采集放大電路,實現(xiàn)心電信號的拾取和預(yù)處理。

通過基于SoC FPGA 的硬件平臺和移植的嵌入式Linux 開發(fā)環(huán)境的軟硬協(xié)同設(shè)計方式,完成了心電信號的A/D 轉(zhuǎn)換、VGA 顯示、Micro SD 卡數(shù)據(jù)存儲和心電信號算法處理,能夠?qū)π碾娦盘栠M行小波分析和QRS 波檢測,實現(xiàn)了對心電信號的采集、顯示、存儲和處理。

心電信號( electrocardiogram,ECG) 能夠客觀反映心臟各部分的生理狀況,也是用來診斷心臟疾病的主要依據(jù),由于其具有易于檢測和有較好直觀性等特點,在臨床醫(yī)學(xué)中得到較為廣泛的研究與應(yīng)用。自1906 年,第一臺心電圖儀用于臨床以來,各種形式的心電監(jiān)護儀相繼出現(xiàn)。傳統(tǒng)的心電圖檢測儀器多以單片機、PC 為核心設(shè)計,系統(tǒng)笨重、檢測手段單一,不利于系統(tǒng)集成度的提高和小型化實現(xiàn),或造成系統(tǒng)的使用不便。由于可穿戴設(shè)備和移動醫(yī)療的興起,心電監(jiān)護儀正向小型化、便攜式、智能化方向發(fā)展。

本文設(shè)計了一種基于片上系統(tǒng)現(xiàn)場可編程門陣列( SoC FPGA) 心電信號檢測處理系統(tǒng),通過A/D 混合設(shè)計和軟硬協(xié)同設(shè)計的方法,實現(xiàn)了心電信號檢測系統(tǒng)。信號采集由模擬前端電路完成,利用SoC FPGA 可重配置和軟硬協(xié)同設(shè)計等優(yōu)勢,通過軟件編程對信號進行A/D 轉(zhuǎn)換、VGA 顯示、數(shù)據(jù)存儲和算法處理,從而實現(xiàn)信號采集、顯示、存儲和處理等多功能集于一體的心電檢測處理系統(tǒng)。

一.心電信號檢測系統(tǒng)設(shè)計

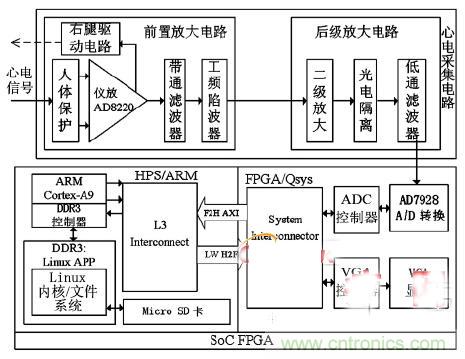

心電信號檢測監(jiān)護系統(tǒng)是一個模擬和數(shù)字的混合系統(tǒng),主要分為體表心電信號采集電路和以SoC FPGA 為核心的心電信號數(shù)字處理系統(tǒng)。采集電路接入醫(yī)用導(dǎo)聯(lián)線通過貼片電極拾取心電信號,心電信號經(jīng)過采集電路放大和模擬濾波處理后進入SoC FPGA,先由HPS 端ARM 嵌入式硬核上基于Linux 的應(yīng)用程序控制進行A/D 轉(zhuǎn)換,轉(zhuǎn)換為數(shù)字信號在FPGA 端進行VGA 顯示,同時將數(shù)字信號傳輸?shù)紿PS 端,可以對數(shù)字信號進行算法處理和存儲到MicroSD 卡上。SoC FPGA 軟硬協(xié)同的開發(fā)方式對硬件設(shè)計和心電信號后續(xù)算法處理的軟件開發(fā)都極為方便。按功能模塊劃分系統(tǒng)整體架構(gòu)如圖1 所示。

圖1 系統(tǒng)框圖

1.體表心電信號采集電路

正常心電信號幅值范圍在10 μV~ 5 mV,典型值為1 mV,頻率范圍在0. 05~ 100 Hz,同時心電信號對噪聲非常敏感。因此,心電信號采集電路需要具備高輸入阻抗、高共模抑制比、低噪聲和低漂移等方面性能。體表心電采集電路由前置放大電路和后級放大電路組成。

2.前置放大電路

前置放大電路主要是對拾取到的心電信號進行初步放大和去噪,以利于后級放大和處理。心電信號中的噪聲主要有工頻干擾、肌電干擾、基線漂移和高頻噪聲。

1) 前置放大電路設(shè)計

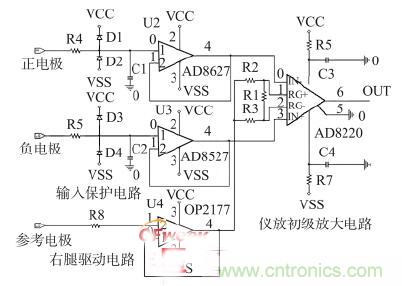

前置放大電路由前級放大電路、帶通濾波電路和50 Hz工頻陷波電路組成,其中,前級放大電路又包括輸入保護電路、右腿驅(qū)動電路和儀表運放放大電路組成,如圖2 所示。

圖2 前置放大電路

由于系統(tǒng)要接到體表采集信號,需要考慮信號采集過程中人體保護的問題,系統(tǒng)中在采集電路的輸入級前端選擇加入耐壓值很高的瞬態(tài)電壓抑制( transient voltage suppressors,TVS) 二極管來保護人體和電路。右腿驅(qū)動電路是在采集心電信號中用于接參考電極,可以有效地消除采集到信號中的共模干擾。儀表運算放大電路完成心電信號的初級放大,同時還要具有高輸入阻抗、高共模抑制比、低噪聲和低漂移的特性。綜合考慮,選擇ADI 公司的精密儀表運放AD8220 芯片,為了防止出現(xiàn)飽和失真,前級增益設(shè)置為20 倍。

2) 工頻干擾和基線漂移的消除

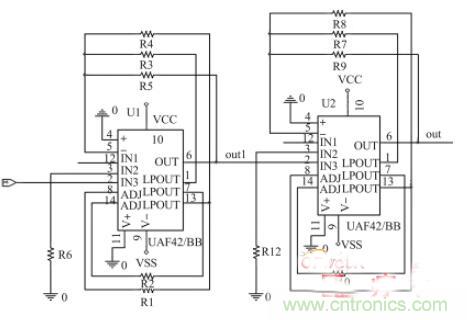

采集電路拾取的心電信號中有低頻的基線漂移和高頻干擾,還有在心電信號頻率范圍內(nèi)的50 Hz 工頻干擾,這些噪聲對心電信號提取的影響非常大。設(shè)計了基于通用有源濾波模塊UAF42 的帶通濾波器和50 Hz 工頻陷波器。帶通濾波器電路的通頻帶為0.05~ 100 Hz,濾除了基線漂移等低頻干擾和高頻噪聲,工頻陷波器能有效濾除工頻噪聲。通過UAF42 可以方便地設(shè)計出各種類型和頻率特性的濾波器,只需要計算出合適阻值的外接電阻器,經(jīng)過簡單的連接就能很好地滿足設(shè)計要求,免去了在有源濾波器的設(shè)計當(dāng)中對電容器、電阻器的選型和匹配的工作。工頻陷波器電路圖如圖3 所示。

圖3 工頻陷波電路

使用兩片UAF42 芯片構(gòu)成4 階陷波器增加陷波深度,設(shè)計工頻陷波電路Q 值為50, 50 Hz 陷波深度為- 110 dB。相比于傳統(tǒng)的雙T 陷波器,此陷波器中心頻率在設(shè)計時就可設(shè)置好,免去了陷波中心頻率的調(diào)試。此外,只需要連接設(shè)計時計算好電阻值的電阻器即可,免去了電容器的選型和匹配。

3.后級放大電路

后級放大電路由二級放大電路、光電隔離電路和低通濾波器電路組成。由于在前置放大電路中,儀表運放的增益值和帶通濾波器的增益值都不能設(shè)得太高,避免噪聲竄入后幅值放大過大和產(chǎn)生振蕩而對有效信號干擾嚴重,所以,總體增益幅度為1 000~ 3 500,放大系統(tǒng)的增益將由多級增益電路實現(xiàn)。二級放大電路能夠?qū)⑾到y(tǒng)的增益達到設(shè)定值,由運放接成電壓負反饋的形式,控制整體電路的增益。光電隔離電路選用了一種低成本的精密電容線性光耦芯片ISO124,實現(xiàn)前后電路的電氣隔離而避免反饋噪聲的影響。低通濾波器主要是為了對由光電耦合引入的高頻噪聲進行消除,避免前級電路的高頻噪聲進入數(shù)字電路板。后級放大電路實現(xiàn)了模擬電路板和數(shù)字電路板的電氣隔離。

4.心電信號SoCFPGA數(shù)字處理系統(tǒng)設(shè)計

1) SoCFPGA的結(jié)構(gòu)和特點

本文設(shè)計使用Altera 公司推出的基于28 nm 工藝的Cyclone V SoC FPGA 作為硬件設(shè)計平臺,這種新型的SoCFPGA 將兩個分立的不同類型的芯片結(jié)合在一起,將基于ARM 的硬核處理器系統(tǒng)( hard processor system,HPS) 集成在FPGA 架構(gòu)中。

使用Altera 公司的嵌入式系統(tǒng)設(shè)計套裝( embedded designsuite,EDS) SoC 進行軟硬件的設(shè)計開發(fā)。用集成QuartusII 中的新一代SOPC 工具Qsys 進行硬件模塊的設(shè)計,它能自動生成互聯(lián)邏輯,連接知識產(chǎn)權(quán)( IP) 功能和子系統(tǒng),SoC EDS 還提供了由Qsys 硬件系統(tǒng)信息轉(zhuǎn)換為軟件開發(fā)所需的工具,使得軟硬件設(shè)計銜接起來,支持Linux 應(yīng)用開發(fā),借助于DS—5 可完成從啟動代碼、內(nèi)核移植到Linux 應(yīng)用程序的軟件設(shè)計。

2) 心電信號數(shù)字處理系統(tǒng)

數(shù)字系統(tǒng)包括A/D 轉(zhuǎn)換模塊、VGA 顯示模塊、數(shù)據(jù)存儲模塊和算法處理模塊。SoC FPGA 中的HPS 和其它的硬件模塊可以通過Qsys 進行配置,用Quartus II 進行硬件設(shè)計,Qsys 和Quartus II 編譯可以產(chǎn)生軟件設(shè)計所需的信息文件。移植嵌入式Linux 系統(tǒng),下載sof 文件,用DS—5 進行基于Linux 的系統(tǒng)軟件工程開發(fā)。

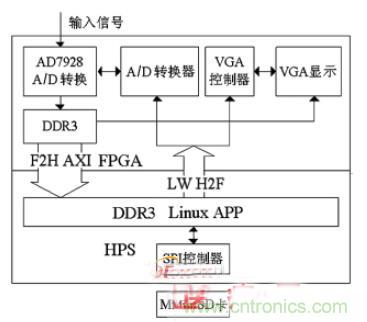

系統(tǒng)的A/D 轉(zhuǎn)換器采用的是ADI 公司的8 通道12 位高精度低功耗A/D 轉(zhuǎn)換芯片AD7928,轉(zhuǎn)換速率為1MSPS。美國心臟學(xué)會推薦的采樣率為500 Hz,但實際中不同應(yīng)用有不同的采樣率,一般為125 ~ 1 000 Hz,監(jiān)護時多采用200 Hz或250 Hz,輔助分析時多用400 ~ 500 Hz,而心電HOLTER 一般取125~ 200 Hz,本系統(tǒng)采用200 Hz。編寫程序控制A/D 轉(zhuǎn)換和數(shù)據(jù)緩存,產(chǎn)生控制VGA 需要的行同步信號與列同步信號,消隱信號、時鐘信號、RGB 信號使屏幕正常工作。嵌入式Linux 文件系統(tǒng)支持Micro SD 卡數(shù)據(jù)的寫入和讀取,將數(shù)字信號通過AXI 橋傳輸?shù)紿PS 端,軟件工程實現(xiàn)心電信號的算法處理和Micro SD 卡數(shù)據(jù)存儲。系統(tǒng)數(shù)字部分結(jié)構(gòu)簡圖如圖4 所示。

圖4 系統(tǒng)數(shù)字部分架構(gòu)

二.系統(tǒng)測試

系統(tǒng)設(shè)計完成后對前端采集電路和整體系統(tǒng)進行調(diào)試和測試。采用三導(dǎo)聯(lián)方式安放醫(yī)用貼片式Ag /AgCl 心電電極,通過醫(yī)用導(dǎo)聯(lián)線連接到心電信號采集系統(tǒng)進行測試。

1.模擬前端采集電路測試

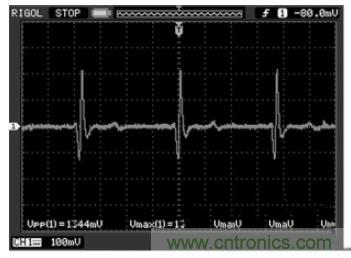

受測者佩戴心電電極,用醫(yī)用導(dǎo)聯(lián)線接入到模擬前端采集電路,后端接入示波器,待信號穩(wěn)定后就可以在示波器上觀測到心電信號波形,圖5 即為模擬前端電路實際測試波形圖。

圖5 模擬前端電路實際測試波形圖

2.系統(tǒng)整體測試

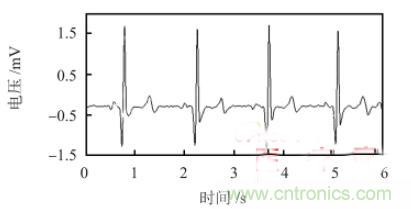

接入整體系統(tǒng),運行軟件工程,系統(tǒng)存儲一段時間的心電信號,取出Micro SD 卡,讀取存儲的數(shù)據(jù)還原后心電信號波形如圖6 所示。

圖6 系統(tǒng)測試心電信號波形

3.心電信號算法處理

心電信號算法處理隨著智能醫(yī)療的應(yīng)用變得越來越廣泛。在健康監(jiān)護和疾病診斷等具體應(yīng)用環(huán)境中,傳統(tǒng)的算法處理都是基于硬件實現(xiàn)的,基于硬件的實現(xiàn)方法一般難度比較大而且耗費資源,嵌入式Linux 系統(tǒng)的移植大大方便了心電信號算法處理的軟件實現(xiàn)。在軟件工程中實現(xiàn)了心電信號的小波去噪和QRS 波檢測。

1)基于小波分析的心電信號去噪

采用小波分析的方法進行心電信號去噪。小波分析由于能同時在時域和頻域中對信號進行分析,具有多分辨分析的功能,所以,在不同的分解層上有效地區(qū)分信號的突變部分和噪聲。對含有噪聲的原始心電信號進行小波分解后,噪聲部分主要集中在高頻小波系數(shù)中,包含有用信號的小波系數(shù)幅值較大,但數(shù)目少;而噪聲對應(yīng)的小波系數(shù)幅值小,數(shù)目較多。基于上述特點,選取無偏似然估計閾值對小波系數(shù)進行處理,然后對信號重構(gòu)即可達到消噪的目的。圖7 為心電信號小波去噪前后對比,信噪比可以達到121 dB。

圖7 心電信號小波去噪

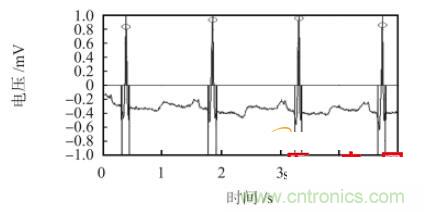

2)基于小波分析的QRS 波檢測

根據(jù)小波變換的理論,信號的奇異點對應(yīng)于其小波變換的一個正模極大值和一個負模極大值對,其位置對應(yīng)于正、負模極大值的過零點,具體算法是尋找小波變換的模最大值,當(dāng)計算的信號模大于一定閾值時,就判定為QRS 波群。同時,這個閾值也是隨著計算結(jié)果自適應(yīng)更新,在判定為QRS 波群后,再檢測過零點則可判定具體的R 波位置。圖8 即為心電信號QRS 波群檢測和R 波峰定位。

圖8 心電信號QRS 波群和R 波峰檢測

對心電信號進行小波分析檢測出R 波波峰等特征點之后可以用提取到的特征值進行模式識別和分類,例如: 利用BP 神經(jīng)網(wǎng)絡(luò)對心電圖ST 段波形進行形態(tài)分類。

三.結(jié)論

本文設(shè)計的基于SoC FPGA 的心電信號檢測系統(tǒng)能夠很好地采集到心電信號,實現(xiàn)了對心電信號的提取、顯示、存儲和處理。測試表明: 系統(tǒng)的模擬前端電路可以采集到比較清晰地放大到合適倍數(shù)的心電信號,系統(tǒng)整體的測試證明了設(shè)計的可行性。SoC FPGA 軟硬結(jié)合的開發(fā)方式能夠?qū)崿F(xiàn)心電信號的算法處理,使設(shè)計更為靈活,為心電信號的處理和分析提供了便利,也為智能醫(yī)療的實現(xiàn)提供了可能性。