【導(dǎo)讀】槽要吐���,文章還是要寫的�。大家知道�����,做一些layout guide是信號(hào)完整性工程師的基本工作之一����,layout guide可以說是一些SI規(guī)則的物理體現(xiàn)���。

前兩天���,跟某友商交流,是一位測(cè)試領(lǐng)域的大牛���,他們也經(jīng)營(yíng)著一個(gè)自媒體。每到大家激起一些火花�����,大牛就會(huì)說“看,又是一篇好文章了吧”��?����?磥泶笈K麄儗懳恼碌膲毫σ埠艽蟀?���,想到這里,小陳不禁潸然淚下���,手一抖�,把抽絲剝繭打成了愁死脖間•••

槽要吐��,文章還是要寫的��。大家知道����,做一些layout guide是信號(hào)完整性工程師的基本工作之一,layout guide可以說是一些SI規(guī)則的物理體現(xiàn)��。某同學(xué)發(fā)現(xiàn)了一份這樣的layout guide:

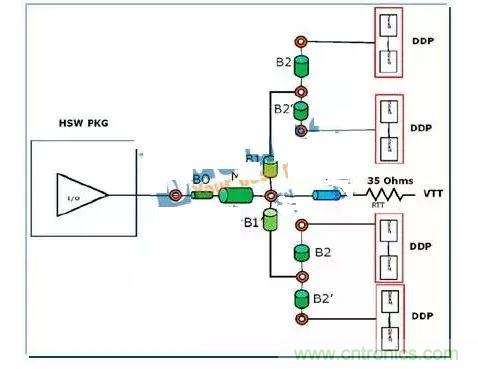

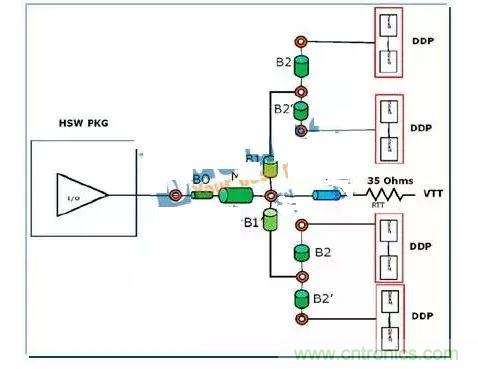

拓?fù)涫沁@樣子的

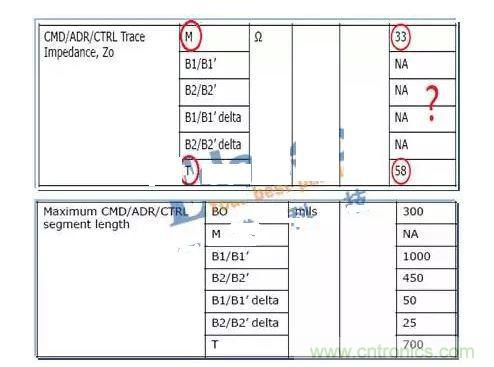

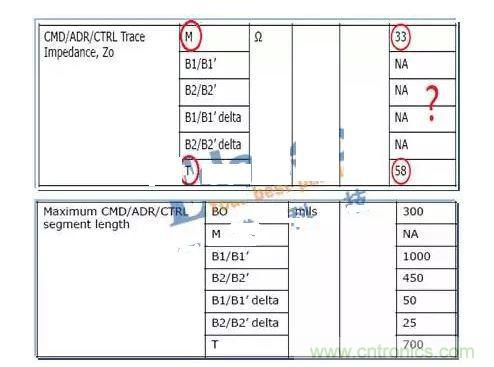

要求是這樣子的

可以看到��,主干段M只有阻抗要求,沒有長(zhǎng)度要求����。而分支B1/B1’/B2/’B2’只有長(zhǎng)度要求沒有阻抗要求,這是為啥�?

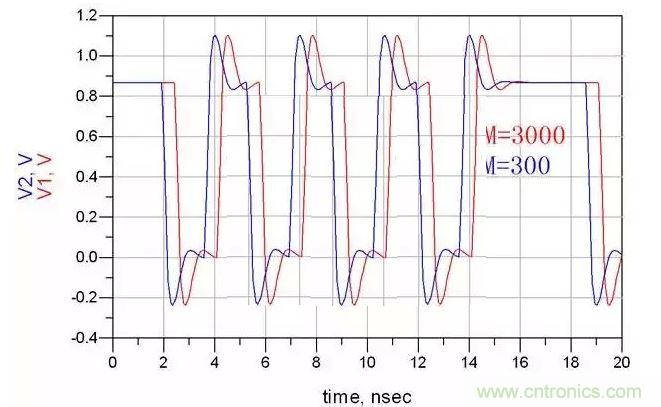

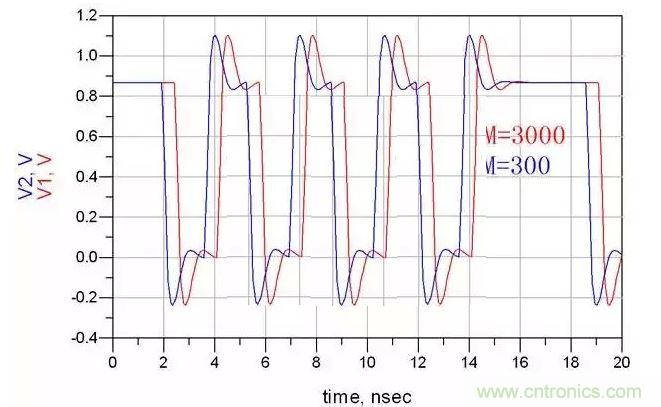

首先,我們知道大部分器件的驅(qū)動(dòng)阻抗是較低的���,這樣減小驅(qū)動(dòng)器本身的分壓����,雖然這樣會(huì)造成較大的源端反射�。而速率越來越高時(shí),需要在功耗和信號(hào)完整性做一個(gè)平衡����,驅(qū)動(dòng)阻抗?jié)u漸的高了起來,而上拓?fù)錇镈DR2�����,驅(qū)動(dòng)阻抗通常在33歐姆左右����,將M段的阻抗控制在33歐姆,則意味著源端反射非常小��,這樣所有進(jìn)入M段往驅(qū)動(dòng)端走的反射信號(hào)全部有去無回��。M段的長(zhǎng)度��,也就不會(huì)對(duì)接收端信號(hào)造成什么影響了��,如下圖:

3

而在M與B/T交界的節(jié)點(diǎn)處�����,反射是不可避免的����。最重要的是第一次從M過來在這個(gè)點(diǎn)的反射,以及第一次從接收端反射回來的能量��,之后的反射波由于分壓以及反射系數(shù)等原因能量是非常小的�����,可以忽略不計(jì)��。

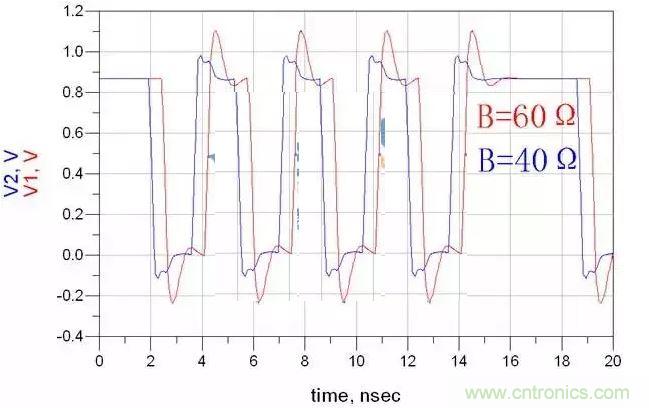

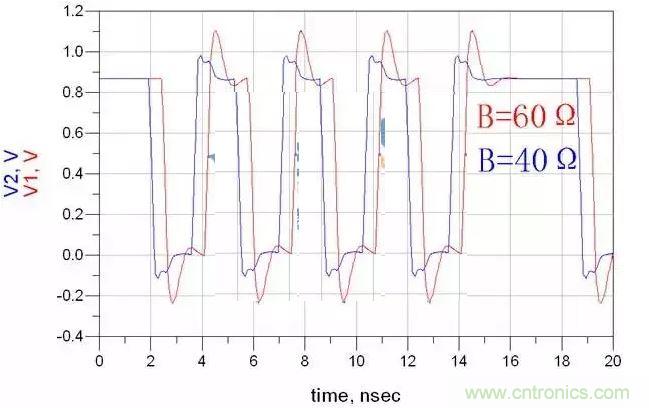

先來看第一次從M過來在這個(gè)點(diǎn)的反射�。我們知道幾個(gè)電阻的并聯(lián)阻抗必定小于其中任意電阻的阻抗�����,傳輸線同理���。假如B段阻抗為60歐姆,從M往接收端看的阻抗為58//60//60≈20歐姆�,反射系數(shù)24%;假如B段阻抗為40��,從M往接收端看的阻抗為58//40//40≈15歐姆���,反射系數(shù)37%�。差別看起來不是特別大�,所以B并沒有明確的阻抗要求,但其實(shí)layout guide里還有一句話���,就是B段走線走越細(xì)越好�。

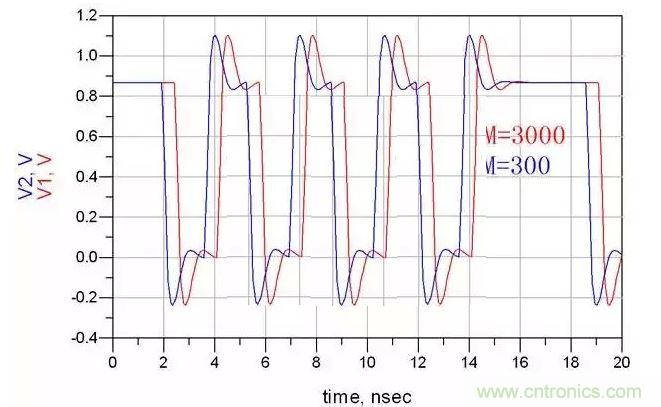

再來看看第一次從接收端反射回來的能量�����,這可就剪不斷理還亂了。不過大家知道�,影響反射的除了阻抗還有走線長(zhǎng)度,走線較短的話����,反射將會(huì)淹沒在上升時(shí)間之中��。我們來看一下線長(zhǎng)符合要求時(shí)阻抗變化的情況:

看來只要分支長(zhǎng)度保證了�����,其實(shí)阻抗影響并不大���。關(guān)于各種拓?fù)?��,可以變的魔術(shù)還是非常多的,layout guide可不是只有“x/x/x/x信號(hào)阻抗控制50Ω”的哦��。