【導讀】電源適配器EMI確實很難理解,很難有精確的紙面設計,但是通過研究我們還是能知道大概趨勢指導設計,而不是一些工程嘴里完全靠trial and error的流程。

這就是我們電源適配器工程師外出機構做測試的實驗室~

我先給出結論,電源適配器EMI確實和開關頻率不成線性關系,某些開關頻率下,EMI濾波器的轉折頻率較高,但是總體趨勢而言,是開關頻率越高,電源適配器EMI體積越?。?/div>

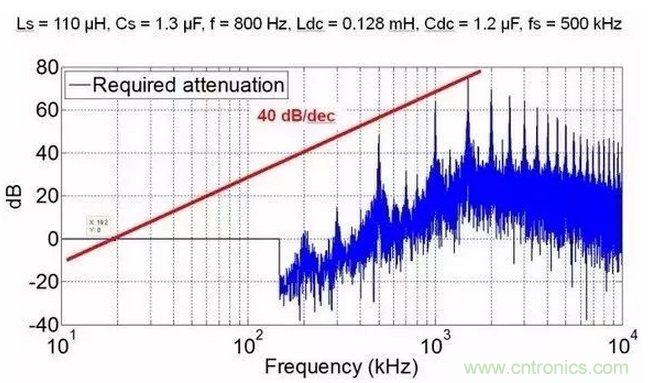

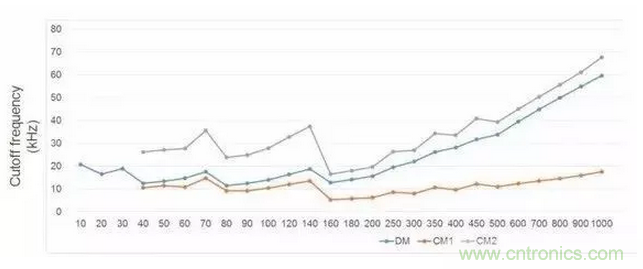

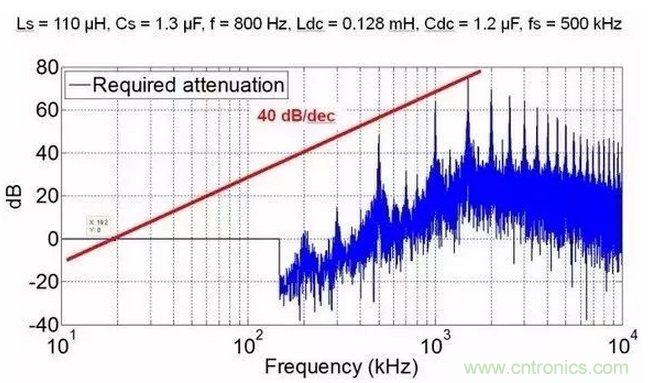

我知道很多人會說,怎么可能,di/dt和dv/dt都大了,怎么可能EMI濾波體積還小了。我想說一句,共模和差模濾波器的沒有區(qū)別,相同的截止頻率下,高頻的衰減更大!就算你高頻下共模噪聲越大,但是你的記住,這個頻率下LC濾波器的衰減更大,想想幅頻曲線吧。為了說明這個結論,我給出一些定量分析結果。這些EMI分析均基于AC/DC三相整流,拓撲為維也納整流。我分別給出了1Mhz和500Khz的共模噪聲,可以看出,500khz共模濾波器需要的截止頻率為19.2kHz,1MHz為31.2kHz。

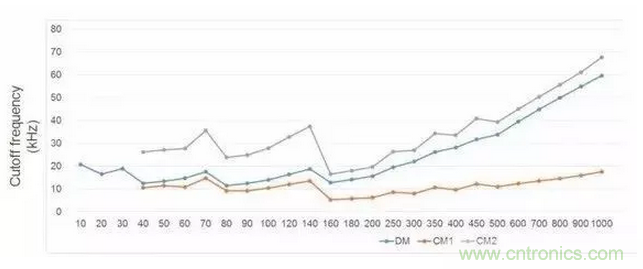

這張圖給出了不同頻率下共模和差模濾波器轉折頻率的關系,可以看出,一些低頻點EMI濾波器體現(xiàn)出了非常好的特性。例如70Khz,140Khz。而這兩個開關頻率是工業(yè)界常用的兩個開關頻率,非常討巧,因為EMI噪聲測試是150KHz到30MHz。不過這個也與拓撲有關。

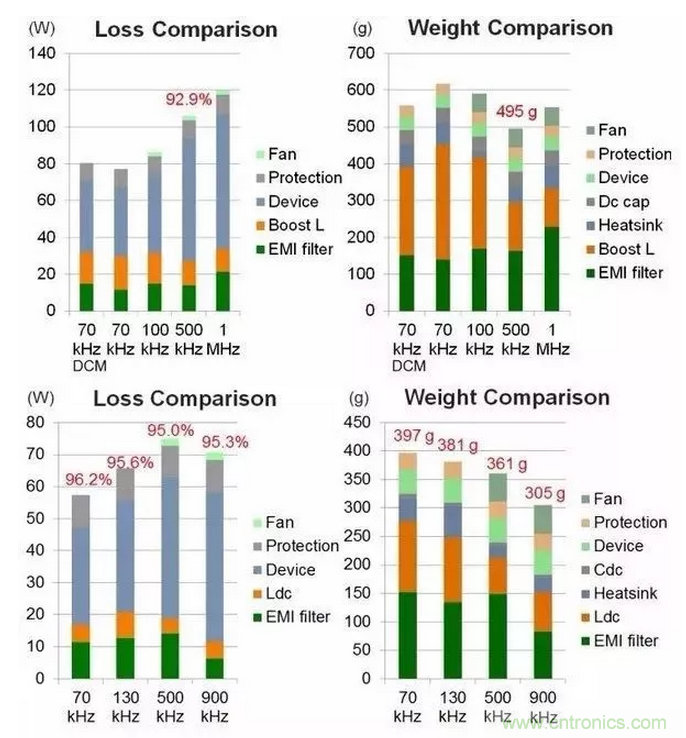

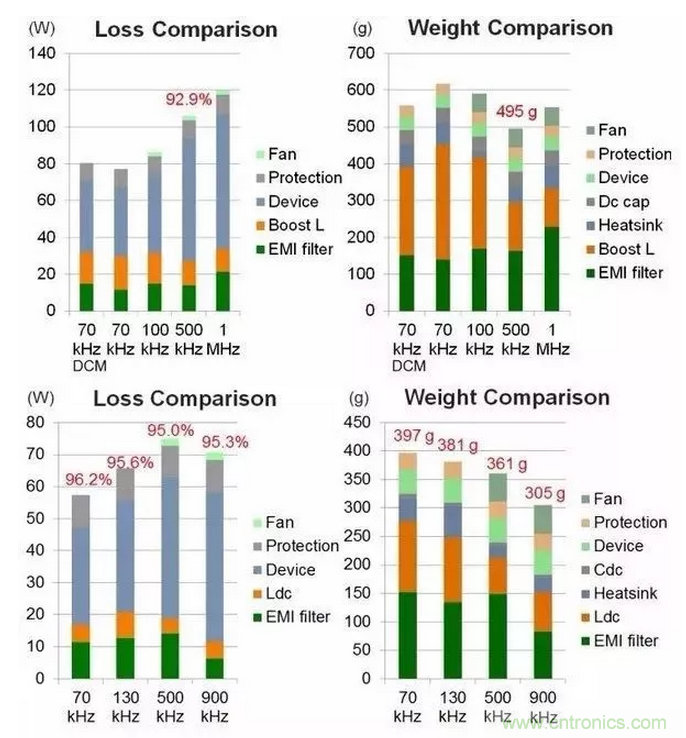

以上數(shù)據均基于仿真,雖然不能精確的反應EMI噪聲的大小,但是趨勢肯定是正確的。說了這么多,我只想表明,開關頻率的選取相當有學問。如果要以高功率密度為設計指標,開關頻率并不是越高越好,而是有一個最佳轉折點。下面2張圖給出了維也納整流器和BUCK-type整流器的功率密度趨勢,可以看出,最佳功率密度點不是一個開關頻率。對那些拍著腦瓜選開關頻率,解決EMI問題的老工程師,我還是懷有很大敬意的,但是我想說的是,如果真正想設計一臺最高功率密度的變換器,詳細的考證是值得的,還不是單純依靠經驗,況且經驗背后也是一定有理論支持。

我不禁問個問題,都有EMI濾波器,EMI噪聲都符合標準,為啥高頻干擾大。難道大家在實際工程遇到高頻干擾是個假象?不是的,舉一個非常簡單的例子,剩下的自己思考吧。

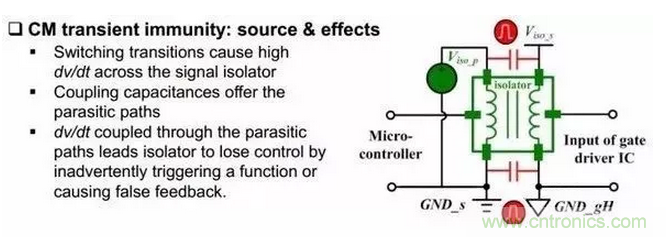

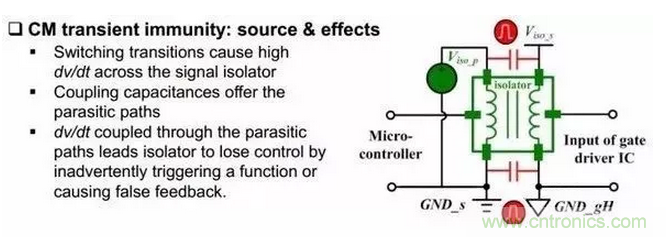

在輸入電壓較高的場合中,一般開關管驅動的都需要隔離。我們知道隔離后一端的地一般要接到懸浮開關管的源端,一般這一點的電平是跳變的,以氮化鎵晶體管為例,這點電壓變化率可以達到140kV/us。而隔離芯片前一端的地是與控制地連接的,你隨便看看隔離模塊電源的手冊,原副邊耦合的寄生電容一般在60pF左右,也是就說在高速開關瞬間,會產生大約6A的電流從副邊的地通過電容耦合到原邊,原邊的地電平肯定瞬間產生尖峰,整個控制系統(tǒng)產生強烈的干擾。所以做高頻的時候,隔離電源的地線千萬不要平行的鋪在2層PCB中,干擾效果會更加強烈。

同時選隔離芯片的時候也需要注意一個參數(shù)叫做CM transient immunity(肯定會給的),這個參數(shù)最好大于開關瞬間,橋臂中點電平的變化速率。光耦隔離這個參數(shù)一般在30kV/us,磁耦在35kV/us,電容耦合在50kV/us(是不是絕望了,都比氮化鎵低,硅器件一般在10kV/us,Sic 30kV/us)。

還有很多細節(jié)可以引起干擾,不過真的不是EMI噪聲作孽。

我們把以上內容簡單總結為:

1、電源適配器不是開關頻率越高,功率密度就越高,目前這個階段來說真正阻礙功率密度提高的是散熱系統(tǒng)和電磁設計(包括EMI濾波器和變壓器)和功率集成技術。

2、慎重選擇開關頻率,開關頻率會極大的影響整個變化器的功率密度,而且針對不同器件,拓撲,最佳的開關頻率是變化的。

3、高頻確實產生很多很難解決的干擾問題,往往要找到干擾回路,然后采取一些措施。

4、為了繼續(xù)維持電力電子變換器功率密度的增長趨勢,高頻肯定是趨勢。只是針對高頻設計的電力電子技術很不成熟,相關配套芯片沒有達到要求,一些高頻的電源適配器電磁設計理論不完善和精確,使用有限元軟件分析將大大增加開發(fā)周期。

希望你我共勉~