【導(dǎo)讀】電容設(shè)計(jì)問題的第一部分��,我們從電源不是必須從濾波電容進(jìn)入芯片管腳開始講起���,帶出了電源供電網(wǎng)絡(luò)(PDN)的阻抗�����。并從頻域角度解釋了濾波電容只是整個(gè)電源供電網(wǎng)絡(luò)的一個(gè)組成部分�。從去耦半徑出發(fā),通過(guò)去耦半徑的計(jì)算,讓大家直觀的看到我們常見的電容的“有效范圍”問題�����。

討論濾波電容的位置與PDN阻抗的關(guān)系����,提出“全局電容”與“局部電容”的概念。能看到當(dāng)電容呈現(xiàn)“全局特性”的時(shí)候�����,電容的位置其實(shí)沒有想象中那么重要�����。

上一個(gè)話題結(jié)束的時(shí)候�����,很多網(wǎng)友提出電容的位置問題:“濾波電容有自己的濾波半徑����,所以重點(diǎn)在于濾波電容正端與芯片電源引腳的距離”。這個(gè)互動(dòng)實(shí)在是配合的太好了�����,高速先生和你握手哈。

傳統(tǒng)的說(shuō)法���,電容有其濾波半徑�,低頻電容濾波半徑大�,所以布局的時(shí)候可以放的稍微遠(yuǎn)一些。并且常規(guī)來(lái)說(shuō)�����,單純?yōu)V波作用的低頻電容不要扎堆布局�����,講究均勻擺放����。而中高頻電容的濾波半徑較小���,需要嚴(yán)格靠近芯片管腳放置���,不能離得太遠(yuǎn)��,要不然電容就“不起作用”了����。

這個(gè)說(shuō)法����,作為我們?yōu)V波電容布局的設(shè)計(jì)指導(dǎo),沒有問題���,依舊是正確的指導(dǎo)原則�,這個(gè)不是我們要討論的設(shè)計(jì)誤區(qū)����。不過(guò)開場(chǎng)白里面說(shuō)了,高速先生����,就是要追根究底,看看電容的濾波半徑到底是怎么回事��?

首先�����,濾波半徑還是基于著名的四分之一波長(zhǎng)理論。(四分之一波長(zhǎng)理論在高速先生的各種文章會(huì)反復(fù)多次出現(xiàn)����,為了方便大家理解,我們會(huì)專題討論各種四分之一波長(zhǎng)的問題�,這里就不再贅述,如果覺得理解這篇文章有問題�,可以單獨(dú)和高速先生進(jìn)行討論) 電容去耦半徑理論認(rèn)為,當(dāng)電容的位置距需要濾波的器件(管腳)的距離剛好是四分之一波長(zhǎng)的時(shí)候�����,電容的補(bǔ)償電流和信號(hào)噪聲電流相位剛好相差180度����,濾波失效。所以為了保證電容的濾波作用����,要求電容的位置距需要濾波的器件(管腳)的距離小于1/10的四分之一波長(zhǎng)���,當(dāng)然����,更嚴(yán)格的要求希望小于1/20的四分之一波長(zhǎng)。

大家看到這���,估計(jì)有點(diǎn)煩躁了���,有的人說(shuō),這個(gè)我早就知道了����。也有人說(shuō),不是叫“看得懂的高速設(shè)計(jì)”嗎,你說(shuō)的這些我看不懂����。那我們就來(lái)看看常見的濾波電容的濾波半徑。(這里我們?yōu)榱擞?jì)算的簡(jiǎn)化���,假設(shè)電容的ESL為0.4NH����,電容的安裝電感為1.5NH。具體的電容安裝電感問題���,在上一個(gè)專題的第四篇文章里面討論過(guò)了���,大家可以參考)

看到這里���,估計(jì)很多PCB設(shè)計(jì)師會(huì)大吃一驚?我們常用的0.1 uf電容����,在考慮四十分之一波長(zhǎng)的時(shí)候,電容的有效去耦半徑居然有12英寸���。就算嚴(yán)格點(diǎn)考慮兩百分之一波長(zhǎng)�,也有將近2英寸的去耦半徑�����。我們?cè)跒V波電容布局的時(shí)候�����,這個(gè)去耦半徑還是問題嗎�?

前面的文章討論過(guò)�����,由于去耦電容只是電源供電網(wǎng)絡(luò)的一部分,同時(shí)高頻噪聲會(huì)更加依賴電源地平板電容及封裝內(nèi)的濾波電容甚至是Die電容來(lái)濾除。10Nf或者更小的1Nf電容��,在電源濾波系統(tǒng)中的作用會(huì)越來(lái)越小�����。在大部分的設(shè)計(jì)中��,0.1 uf電容就是板級(jí)系統(tǒng)設(shè)計(jì)的時(shí)候��,電源濾波系統(tǒng)中用到的最“高頻”的電容了����。

借這個(gè)機(jī)會(huì),再和大家討論下高速先生討論P(yáng)CB設(shè)計(jì)誤區(qū)的出發(fā)點(diǎn):很多理論其實(shí)沒有錯(cuò)���,只是我們?cè)谑褂玫臅r(shí)候沒有真正知其所以然�,所以設(shè)計(jì)中想當(dāng)然的“過(guò)設(shè)計(jì)”很多。這類“過(guò)設(shè)計(jì)”有時(shí)候并沒有壞處��,只是當(dāng)設(shè)計(jì)出現(xiàn)“惡劣”情況并需要“取舍”的時(shí)候��,會(huì)造成一些困難��。

比如電容的去耦半徑問題�,大家都有這個(gè)概念,然后都知道“小”電容(高頻電容)的去耦半徑很小���,需要嚴(yán)格靠近芯片管腳��。這個(gè)設(shè)計(jì)原則沒有錯(cuò)誤�,只是當(dāng)數(shù)碼消費(fèi)類產(chǎn)品由于更小的面積����,更低的成本以及結(jié)構(gòu)的要求(如厚度),需要我們把電容單面布局�����,放在和BGA的同一面的時(shí)候��,很多人困惑了����,電容離芯片的電源管腳這么遠(yuǎn)(有時(shí)還要考慮3mm或者5mm的返修間距,就更遠(yuǎn)了)���,電容還能起作用嗎��?

由此引申的另一個(gè)問題�,和我們的這次的主題相關(guān)�����,先提前預(yù)告一下:我們做設(shè)計(jì)的時(shí)候��,很喜歡把同種類的數(shù)字電源��,對(duì)不同芯片進(jìn)行供電的時(shí)候���,用磁珠隔離一下���,希望能避免不同芯片之間同種電源的干擾。電容的作用范圍這么大����,磁珠隔離了“想象中”的芯片間電源軌道的干擾的同時(shí)�,會(huì)不會(huì)也阻礙了電容的作用呢����?

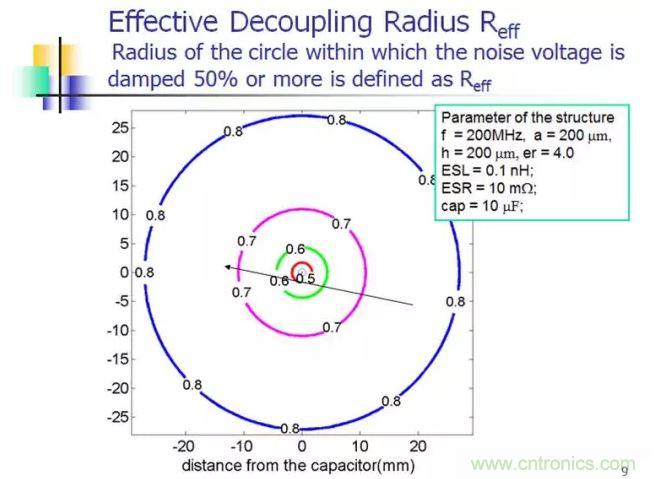

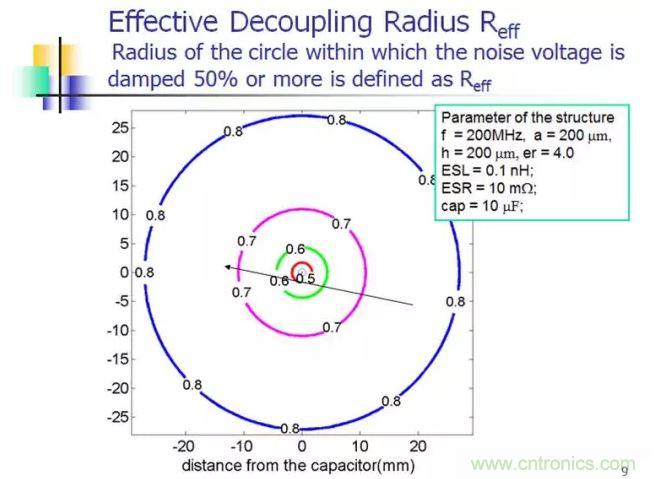

本節(jié)的結(jié)尾,再給大家看一個(gè)圖片��,也是關(guān)于電容的去耦半徑和作用范圍的��。之前討論的諧振頻率的四分之一波長(zhǎng)����,還是有局限性的,首先電容起作用的最高頻率不止是諧振頻率�。其次,作用范圍還得考慮你設(shè)定的濾波效率����。理論是復(fù)雜的,任重而道遠(yuǎn)��,多前進(jìn)一些����,真相就更清晰一點(diǎn)��。

當(dāng)然�����,本節(jié)的結(jié)論還是繼續(xù)有效的,我們常用的0.1uf電容����,濾波半徑遠(yuǎn)遠(yuǎn)比我們想象的要大。