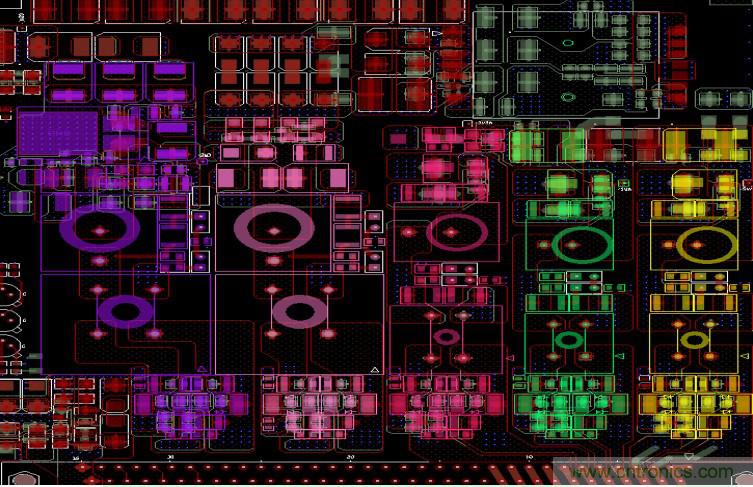

【導(dǎo)讀】當(dāng)我們對整個電路原理分析好以后,就可以開始對整個電路進(jìn)行布局布線,這一期,給大家介紹一下布局的思路和原則。

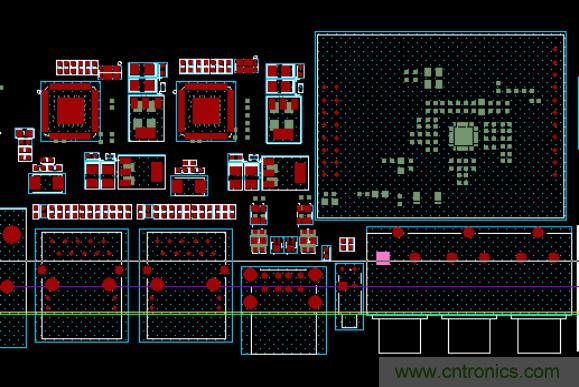

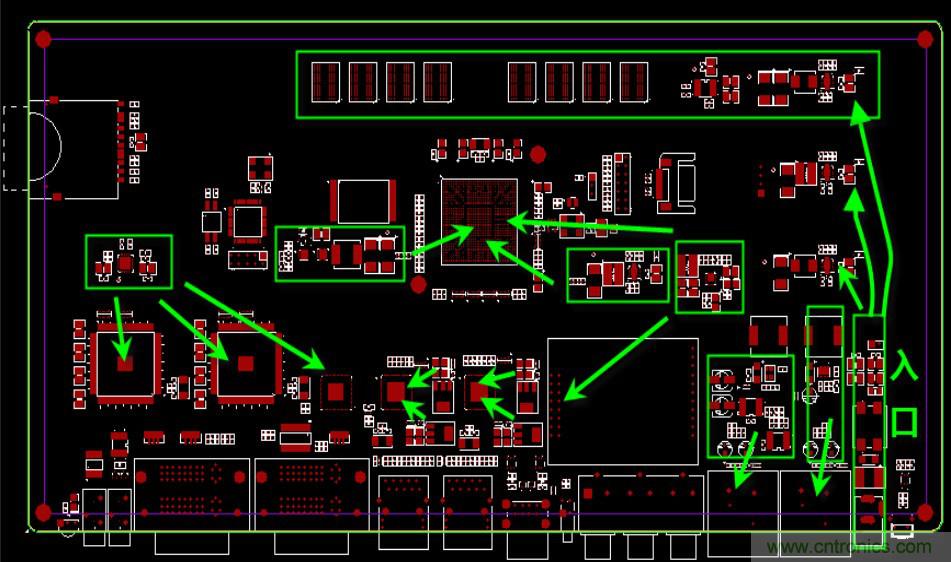

1、首先,我們會對結(jié)構(gòu)有要求的器件進(jìn)行擺放,擺放的時候根據(jù)導(dǎo)入的結(jié)構(gòu),連接器得注意1腳的擺放位置。

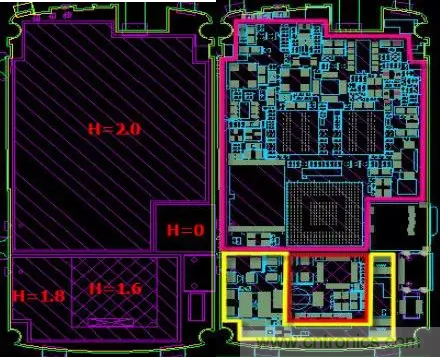

2、布局時要注意結(jié)構(gòu)中的限高要求。

3、 如果要布局美觀,一般按元件外框或者中線坐標(biāo)來定位(居中對齊)。

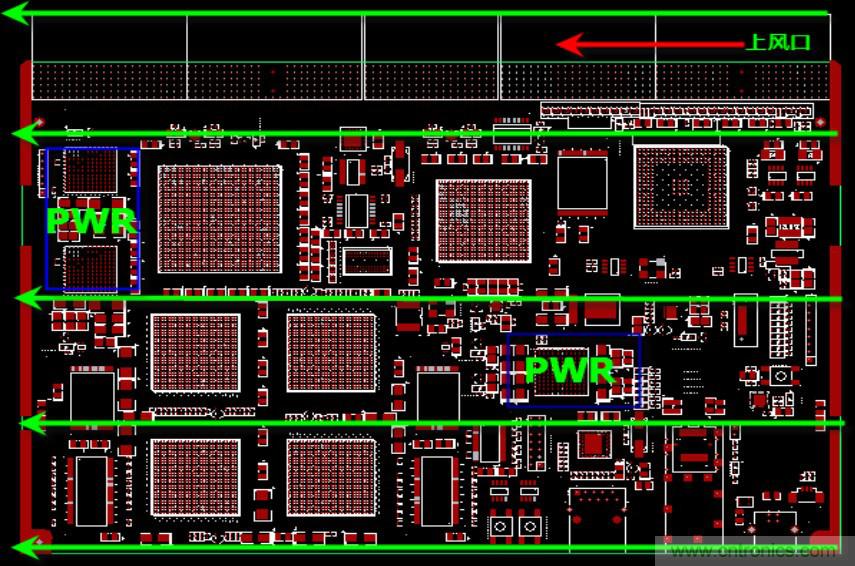

4、 整體布局要考慮散熱。

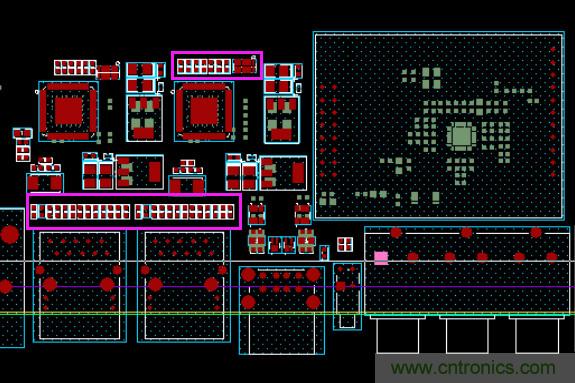

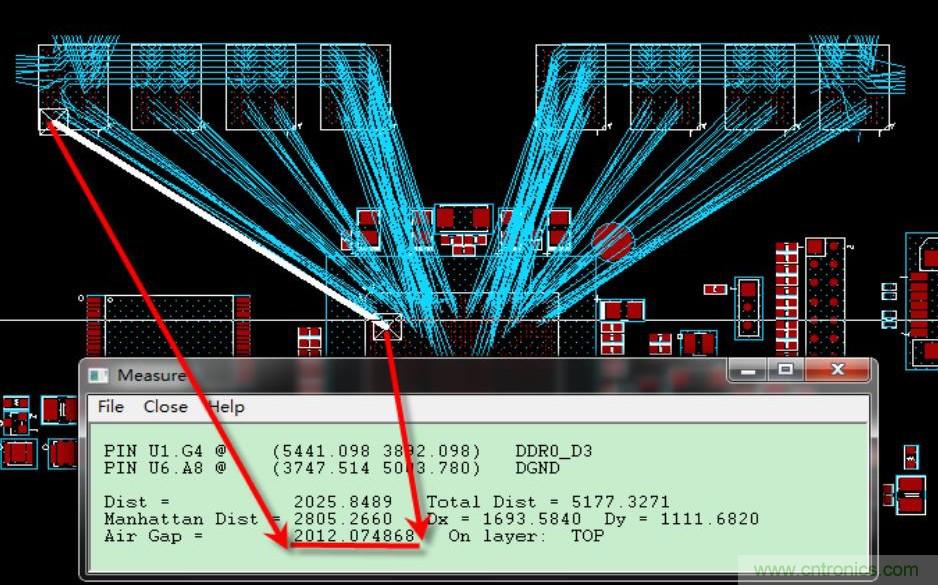

5、 布局的時候需要考慮好布線通道評估、考慮好等長需要的空間。

6、 布局時需要考慮好電源流向,評估好電源通道。

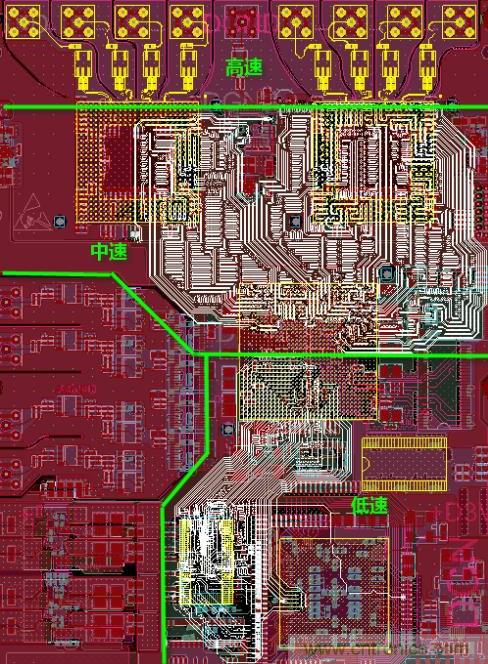

7、 高速、中速、低速電路要分開。

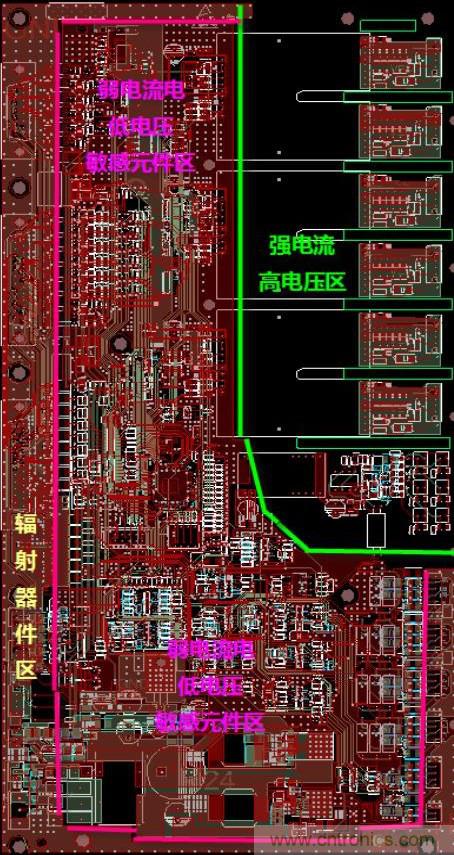

8、強電流、高電壓、強輻射元器件遠(yuǎn)離弱電流、低電壓、敏感元器件。

9、 模擬、數(shù)字、電源、保護(hù)電路要分開。

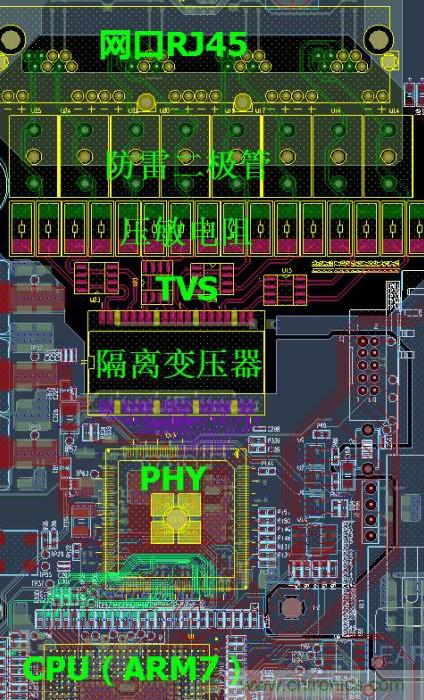

10、 接口保護(hù)器件應(yīng)盡量靠近接口放置。

11、 接口保護(hù)器件擺放順序要求:

(1)一般電源防雷保護(hù)器件的順序是:壓敏電阻、保險絲、抑制二極管、EMI濾波器、電感或者共模電感,對于原理圖 缺失上面任意器件順延布局;

(2)一般對接口信號的保護(hù)器件的順序是:ESD(TVS管)、隔離變壓器、共模電感、電容、電阻,對于原理圖缺失上面任意器件順延布局;嚴(yán)格按照原理圖的順序(要有判斷原理圖是否正確的能力)進(jìn)行“一字型”布局。

12、電平變換芯片(如RS232)靠近連接器(如串口)放置。

13、 易受ESD干擾的器件,如NMOS、 CMOS器件等,盡量遠(yuǎn)離易受ESD干擾的區(qū)域(如單板的邊緣區(qū)域)。

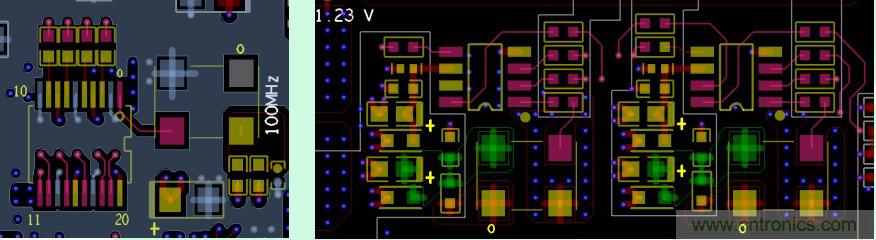

14、 時鐘器件布局:

(1)晶體、晶振和時鐘分配器與相關(guān)的IC器件要盡量靠近;

(2)時鐘電路的濾波器(盡量采用“∏”型濾波)要靠近時鐘 電路的電源輸入管腳;

(3)晶振和時鐘分配器的輸出是否串接一個22歐姆的電阻;

(4)時鐘分配器沒用的輸出管腳是否通過電阻接地;

(5)晶體、晶振和時鐘分配器的布局要注意遠(yuǎn)離大功率的元器件、散熱器等發(fā)熱的器件;

(6)晶振距離板邊和接口器件是否大于1inch。

15、開關(guān)電源是否遠(yuǎn)離ADDA轉(zhuǎn)換器、模擬器件、敏感器件、時鐘器件。

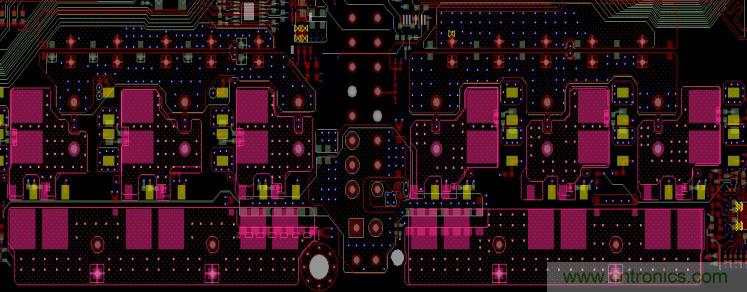

16、開關(guān)電源布局要緊湊,輸入輸出要分開, 嚴(yán)格按照原理圖的要求進(jìn)行布局,不要將開關(guān)電源的電容隨意放置。

17、 電容和濾波器件 :

(1)電容務(wù)必要靠近電源管腳放置,而且容值越小的電容要越靠近電源管腳;

(2)EMI濾波器要靠近芯片電源的輸入口;

(3)原則上每個電源管腳一個0.1uf的小電容、一個集成電路一個或多個10uf大電容,可以根據(jù)具體情況進(jìn)行增減;

推薦閱讀: