【導讀】大家都知道,電源效率對于便攜式設(shè)備以及模擬IC的噪聲抗擾度來說都非常重要。本文主要介紹電壓參考電路,其不僅支持極低的工作靜態(tài)電流(低于250nA),而且還符合標準CMOS工藝。

這種電路針對各種應用進行了優(yōu)化設(shè)計,適合便攜式電子設(shè)備、汽車、醫(yī)療設(shè)備,以及高電源抑制比 (PSRR) 和開關(guān)噪聲抗擾度都非常重要的片上系統(tǒng) (SoC) 實施。

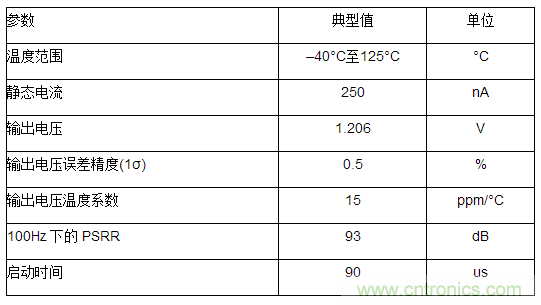

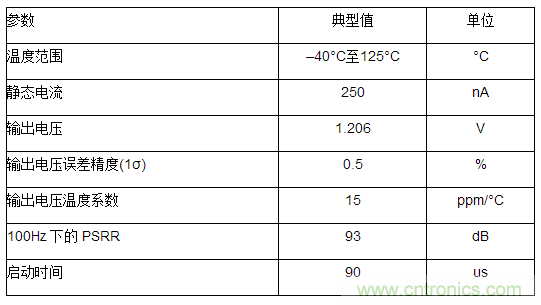

上述電壓參考在低頻率下支持90dB。輸出電壓變化的標準偏差是 0.5%,在–40℃至125℃溫度范圍內(nèi)的溫度系數(shù)為15ppm/℃。這些特性可在1.6V至5.5V的電源電壓范圍內(nèi)實現(xiàn)??蓪嵤└鞣N用于為電壓參考實現(xiàn)輸入噪聲抗擾度的方法。

介紹

幾乎每款模擬電路都需要高精度高穩(wěn)定參考電壓或電流源。不過,在選擇片上系統(tǒng)(SoC) 技術(shù)時,參考電壓模塊不應成為限制因素。也就是說這類系統(tǒng)所選用的技術(shù)工藝對于參考電壓源來說并不一定總是最理想的。因此,其設(shè)計應該更穩(wěn)健,才能適應各種技術(shù)工藝的變化。

電池通常可作為SoC的電源。這就更需要提高工作在大電源電壓范圍內(nèi)的電壓參考源的線性穩(wěn)壓性能。要延長電池使用壽命,就需要低靜態(tài)電源電流。同時,還需要在寬泛頻率下實現(xiàn)高電源抑制比(PSRR),以抑制來自高速數(shù)字電路、降壓轉(zhuǎn)換器或片上其它開關(guān)電路的噪聲。本文主要介紹具有高PSRR的超低靜態(tài)電流帶隙電壓參考。

基本帶隙電壓參考結(jié)構(gòu)

改善 PSRR的主題思想是在低壓降穩(wěn)壓器(LDO)后面布置一個帶隙電壓源。現(xiàn)有線性穩(wěn)壓器拓撲在靜態(tài)電流、DC負載穩(wěn)壓、瞬態(tài)響應、去耦電容以及硅芯片面積要求方面存在很大差異。由于我們的目標是在沒有外部電容器的情況下,在同一芯片上提供全面集成型 LDO,因而典型LDO結(jié)構(gòu)并不適合。

這些結(jié)構(gòu)與超低靜態(tài)電源電流相矛盾。為了緩解這一矛盾,您可為LDO 使用與參考源相同的帶隙。不宜采用標準LDO結(jié)構(gòu)的原因在于它需要輸出電容器來實現(xiàn)穩(wěn)定工作。最佳選項是帶一個增益級的結(jié)構(gòu),其無需輸出電容器便可實現(xiàn)穩(wěn)定。

低壓降穩(wěn)壓器

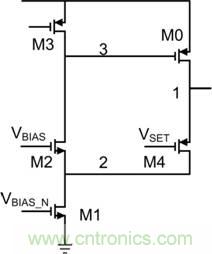

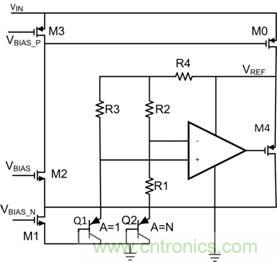

圖1是該設(shè)計[1]中所使用LDO的內(nèi)核及其簡化原理圖。圖1[2]中的M0和M4代表翻轉(zhuǎn)電壓跟隨器(FVF),其可實施無逆向功能及相關(guān)極點的單級穩(wěn)壓。靜態(tài)電流由晶體管M1和M3確定。晶體管M2 可作為共柵放大器。

LDO的開環(huán)增益由第一個級聯(lián)級(即晶體管M2和M3)決定??勺鳛樨撦d的 M4 PMOS跟隨器存在低阻抗源,因此 FET M0的輸出增益接近1。在圖2中的小型信號等效電路的幫助下,對所推薦的 LDO結(jié)構(gòu)進行穩(wěn)定性分析,結(jié)果顯示只有一個極點(公式1):

可作為補償電容器的M0柵源電容器可創(chuàng)建 LDO的主極點。因此無需去耦片外電容器,便可使LDO[3]穩(wěn)定。

圖1:具有翻轉(zhuǎn)電壓跟隨器、無輸出電容器的LDO

圖2:LDO的小型信號等效電路

這種LDO的另一項優(yōu)勢是簡單的自啟動程序,其無需專用電路。最初,在電壓VDD 為 0 時,VOUT也為 0,跟隨器M4 在無反饋的情況下關(guān)閉,M1的偏置電流大于M3的偏置電流。因此,柵極電壓M0 不僅可降低,而且還可驅(qū)動輸出電壓VOUT至所選的輸出電壓值。

這種架構(gòu)的缺點是線路穩(wěn)壓及 PSRR差。原因在于低開環(huán)增益,因為它僅由一個增益級決定。合理的解決方案可能是第一級的級聯(lián)電流源,其可提高增益,進而可提高線路穩(wěn)壓性能和PSRR。

圖1中的LDO輸出電壓為(公式2):

其中,VSET為參考電壓,VGS,M4是M4的柵源電壓。

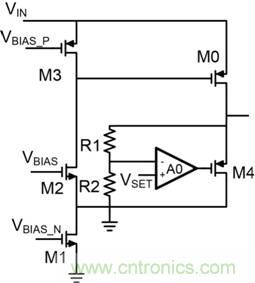

因此,輸出電壓對溫度和工藝變化極為敏感。要避免這種問題,就必須創(chuàng)建一個更為理想的跟隨器,其中 M4 是反饋環(huán)路的一部分(圖3)。

圖3:M4位于放大器反饋環(huán)路中、無輸出電容器的LDO。

這種情況下的輸出電壓為公式3:

其中,A0是放大器的開環(huán)增益反饋。對于高反饋放大器增益而言,可使用公式4:

圖4:具有電阻式分壓器、M4位于放大器反饋環(huán)路、無輸出電容器的 LDO

在反饋環(huán)路(圖4)中添加電阻式分壓器后,輸出電壓轉(zhuǎn)變?yōu)椋?/div>

VOUT=VSET(1+R1/R2)

FVF反饋放大器不影響整體 LDO穩(wěn)定性,因為它位于主LDO反饋環(huán)路的外部。對于本地反饋環(huán)路而言,只要求設(shè)計方案穩(wěn)定。

[page]

帶隙內(nèi)核說明

所選用的帶隙內(nèi)核(圖5)采用在標準CMOS 技術(shù)中廣泛使用的經(jīng)典結(jié)構(gòu)。

圖5:所推薦帶隙電壓參考內(nèi)核的簡化方框圖

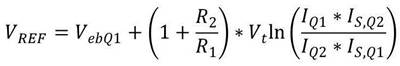

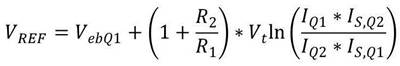

通過添加雙極性晶體管的負溫度系數(shù)基射極間電壓,可獲得帶隙電壓的低溫系數(shù),從而可通過在不同電流密度下偏置的兩個基射極間電壓之差獲得正溫度系數(shù)電壓。為電阻器R2和R3選擇相等的值,參考電壓就可表示為公式5:

其中VEB是Q1的基射極間電壓,VT是熱電壓,IQ1和IQ2是通過晶體管Q1和Q2的電流,而 IS,Q1和IS,Q2則分別是Q1和Q2的飽和電流。

誤差源

要為任何帶隙電壓參考實現(xiàn)良好的精確度,必須定義總體精度誤差的主要形成因素[4]。以下是所推薦架構(gòu)的最大誤差源:

放大器失調(diào)電壓

電阻器R1與R2之間的不匹配

雙極性晶體管的飽和電流不匹配

電阻器R1、R2和R3的變化

放大器失調(diào)電壓

放大器失調(diào)電壓對于參考電壓精確度來說很關(guān)鍵,因為它通過與發(fā)射-基極電壓差相同的方式放大。盡管我們可以通過增大雙極性晶體管的面積比來減少對放大器失調(diào)電壓的影響,但由于電壓差具有對數(shù)尺度,因此我們會受到這個比例的合理值限制。在本例中,我們選擇的比例為24。

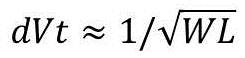

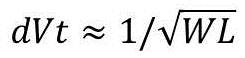

對放大器失調(diào)電壓影響最大的是輸入級晶體管閥值電壓變化。它可通過增大放大器輸入對的尺寸來改善(公式6)。

電阻器R1與R2之間的不匹配

電阻器R1與R2之比可定義公式5中正溫度系數(shù)項的增益。為了讓該增益系數(shù)準確,我們使用較大面積單位電阻器。使用特殊的電阻器布局,可實現(xiàn)0.1%的誤差比例精度。

雙極性晶體管的電阻器與飽和電流的變化

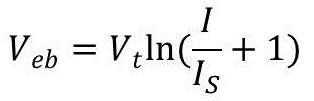

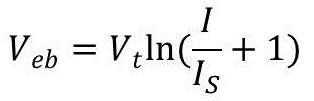

這兩種變化會導致雙極性晶體管的基極-發(fā)射極電壓Veb發(fā)生偏移?;鶚O-發(fā)射極電壓可按公式7確定:

其中,I是發(fā)射極電流,IS是雙極性晶體管的飽和電流。引起IS變化的主要原因是Q1和Q2晶體管面積的不匹配以及雜質(zhì)濃度的變化。

電阻器R1的變化可影響通過晶體管Q2 的電流I的絕對值,它是負溫度系數(shù)項VEB的一部分。

電阻器R2和R3分別可確定通過Q1和Q2 的電流值。R2和R3的變化可導致參考電壓(公式5)的正溫度系數(shù)不準確。不過,可通過對電阻器R2與R3進行良好匹配來降低該變化所引起的誤差。

高PSRR帶隙電壓參考電路

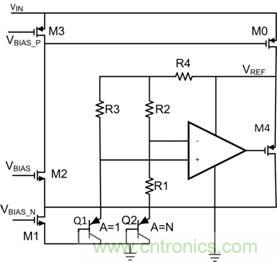

由于上述傳統(tǒng)電壓參考架構(gòu)的所有缺點,我們建議采用改進的電壓參考,它是帶隙電壓參考與低壓降穩(wěn)壓器的整合解決方案(圖6)。

圖6:帶隙電壓參考結(jié)合低壓降穩(wěn)壓器的方框圖

該示例中的輸出電壓可由公式8確定:

VREF節(jié)點既是帶隙參考的輸出節(jié)點,同時也是帶隙核心電路的電源線。這有助于我們通過 LDO保護帶隙核心電路免受電源電壓紋波影響。

要獲得小靜態(tài)電流,電阻器 R1、R2、R3和R4的值就會比較大,推薦電路的電阻為8MΩ。這可使通過 Q1和Q2的電流降低至 40nA。推薦架構(gòu)的整體靜態(tài)電流為250nA。除此之外,我們還可采用一款靜態(tài)電流為100nA的偏置電流電源。

偏置電流電路

所推薦的偏置電流電路基于一種著名的電路結(jié)構(gòu)(如圖7所示),在參考文獻5[5]中有詳細介紹。

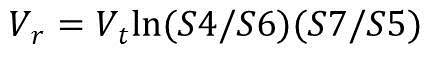

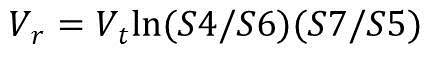

在該電路中,兩個N型晶體管M5和M7構(gòu)成第一個增益為S7/S5 的電流鏡,而兩個P型晶體管M4和M6 則構(gòu)成第二個增益為S4/S6 的電流鏡,其中S4、S5、S6和S7是相應晶體管的面積。

偏置發(fā)生器通常不需要特別啟動電路,這可減少靜態(tài)電流和占用面積。如果電流足夠小,電阻R 就可以忽略。由M5/M7和M4/M6構(gòu)成的兩個電流鏡可互連成一個閉環(huán)。

該環(huán)路增益大于單位增益,因此兩個分支中的電流都會增大,直至達到均衡為止。這將由電阻R的壓降定義,可表示為公式9:

圖7:具有動態(tài)啟動電流的偏置生成器

要加快啟動速度并避免可能的漏電影響,可使用一款附加啟動電路。晶體管M0 可作為具有極大電阻的橫向雙極性 NPN晶體管使用,其可最大限度地降低啟動電流。電容器 C 不僅可在電路加電時提供快速瞬態(tài)啟動,而且還可防止啟動電路發(fā)生振蕩。在啟動之后,電路由晶體管M2阻斷。偏置模塊的偏置電流是40nA??偭骱氖?80nA。

[page]

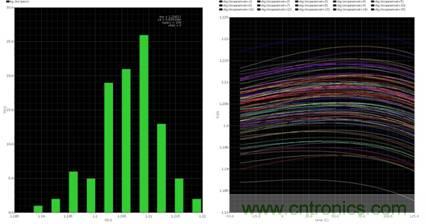

驗證結(jié)果

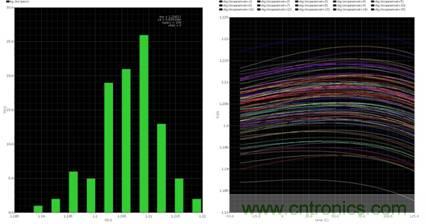

所推薦帶隙參考不僅可用于超低噪聲、高PSRR的低壓降穩(wěn)壓器,而且還可采用CMOS 9T5V 技術(shù)實施。PSRR值如圖8所示,輸出電壓精度的蒙特卡洛溫度變化仿真結(jié)果如圖9所示。測量結(jié)果請參見表1。

圖8:電壓參考源的PSRR

圖9:輸出電壓精度

表1.測量數(shù)據(jù)

總結(jié)

我們不僅介紹了采用 CMOS9T5V 0.18μm工藝實施的、高PSRR 的極低功耗帶隙電壓參考,而且還詳細介紹了最大限度降低功耗和最大限度提高PSRR的設(shè)計條件。將帶隙電壓參考與低壓降穩(wěn)壓器相結(jié)合,可在100Hz下獲得93dB的高PSRR。該電路的最大靜態(tài)電流僅為250nA,是超低功耗應用最具吸引力的選擇。

參考文獻

J. Guo和K. N. Leung,《采用 90 納米 CMOS工藝技術(shù)實施的、無輸出電容器的小型 6uWLDO》,摘自《IEEE固態(tài)電路雜志》2010年9月第 48卷第 9 號;

Blakiewicz, G.,《支持更快時間響應的CMOS低壓降穩(wěn)壓器》,摘自《2011年第18屆國際大會會議記錄 — 集成電路與系統(tǒng)混合設(shè)計 (MIXDES)》2011年6月16 ~ 18 日第 ××卷第 ×× 號的第 279 頁 ~ 282 頁;

P. Hazucha、T. Karnik、B. A. Bloecher、C. Parsons、D. Finan 和 S. Borkar,《支持超快負載調(diào)節(jié)的小型線性穩(wěn)壓器》,摘自《IEEE固態(tài)電路雜志》2005 年 4 月第 45 卷第 4 號;

S. Strik,《帶隙電壓參考:誤差及其最小化方法》,摘自《BEC 2006會議記錄》2006年10月2日第 123 頁 ~ 126頁;

E. Vittoz 與 J. Fellrath,《基于弱反向工作的CMOS模擬集成電路》,摘自《IEEE固態(tài)電路雜志》1977年6月SC-12卷第 3 號;

如欲了解有關(guān)LDO的更多詳情,敬請訪問:www.ti.com/ldo-ca。